西門子6ES7318-3EL01-0AB0

解釋

多級(jí)放大時(shí),,防止信號(hào)通過公共電源電阻耦合到前級(jí)放大的一種方法,。由于這種耦合而構(gòu)成反饋,將在某一頻率上產(chǎn)生自激,,在接有喇叭時(shí)會(huì)產(chǎn)生汽笛聲,。一般用與機(jī)內(nèi)電源相串聯(lián)或并聯(lián)的rc濾波網(wǎng)絡(luò)來實(shí)現(xiàn)。

作用

防止發(fā)生不可預(yù)測的反饋,,影響下一級(jí)放大器或其它電路正常工作,。

例如

使用一個(gè)共發(fā)射極接法三極管,由于Vcc有內(nèi)阻,,當(dāng)基極輸入交流信號(hào),,會(huì)在電源Vcc電流(基極集電極電流和)產(chǎn)生交流電流,從而影響偏置端基極,。導(dǎo)致輸出端電壓不穩(wěn)定,。通常的解決辦法是使用電容對(duì)Vcc交流接地,去除此影響,。這個(gè)解決辦法叫做去耦,。

去耦:專指去除芯片電源管管腳上的噪聲,該噪聲是芯片本身工作產(chǎn)生的,。

在直流電源回路中,負(fù)載的變化會(huì)引起電源噪聲,。例如在數(shù)字電路中,,當(dāng)電路從一個(gè)狀態(tài)轉(zhuǎn)換為另一種狀態(tài)時(shí),就會(huì)在電源線上產(chǎn)生一個(gè)很大的尖峰電流,,形成瞬變的噪聲電壓,。配置去耦電容可以抑制因負(fù)載變化而產(chǎn)生的噪聲,是抑制電路板的可靠性設(shè)計(jì)的一種常規(guī)做法,。

配置原則

●電源輸入端跨接一個(gè)電解電容器,,如果印制電路板的位置允許,采用比較大的電解電容器的抗干擾效果會(huì)更好,。

●為每個(gè)集成電路芯片配置一個(gè)0.01uF的陶瓷電容器,。如遇到印制電路板空間小而裝不下時(shí),可每4~10個(gè)芯片配置一個(gè)1~10uF鉭電解電容器,,這種器件的高頻阻抗特別小,,在500kHz~20MHz范圍內(nèi)阻抗小于1Ω,而且漏電流很?。?.5uA以下),。

●對(duì)于噪聲能力弱、關(guān)斷時(shí)電流變化大的器件和ROM,、RAM等存儲(chǔ)型器件,,應(yīng)在芯片的電源線(Vcc)和地線(GND)間直接接入去耦電容。

●去耦電容的引線不能過長,,特別是高頻旁路電容不能帶引線,。

西門子6ES7318-3EL01-0AB0

諧振現(xiàn)象是交流電路中產(chǎn)生的一種特殊現(xiàn)象,對(duì)諧振現(xiàn)象的研究有著重要的意義,。在實(shí)際電路中,,它既被廣泛地應(yīng)用,有時(shí)又需避免諧振情況發(fā)生,。

對(duì)于無源一端口網(wǎng)絡(luò),,它的入端阻抗或?qū)Ъ{的值通常與電路頻率有關(guān)。一個(gè)包含有電感和電容的無源一端口網(wǎng)絡(luò),,其入端阻抗或?qū)Ъ{一般為一復(fù)數(shù),。但在某些特定的電源頻率下,其入端阻抗或?qū)Ъ{的虛部可能變?yōu)榱?,此時(shí)阻抗或?qū)Ъ{呈純電阻特性,,使端口電壓與電流成為同相。無源一端口網(wǎng)絡(luò)出現(xiàn)這種現(xiàn)象時(shí)稱為處于諧振狀態(tài)。下面分別討論串聯(lián)諧振與并聯(lián)諧振現(xiàn)象,。

圖1

圖1為電阻,、電感和電容的串聯(lián)電路,當(dāng)外施的正弦電壓角頻率為 時(shí),,它的入端阻抗為:

時(shí),,它的入端阻抗為:

(1)

(1)

由式可見,,RLC串聯(lián)電路中感抗 與容抗

與容抗 是直接相減的。一般情況下

是直接相減的。一般情況下 ,,即

,,即 ,,則阻抗的虛部

,,則阻抗的虛部 不為零,阻抗角也不為零,,此時(shí)端電壓與電流不同相,。當(dāng)激勵(lì)電壓的角頻率變化時(shí),感抗

不為零,阻抗角也不為零,,此時(shí)端電壓與電流不同相,。當(dāng)激勵(lì)電壓的角頻率變化時(shí),感抗 與容抗

與容抗 都發(fā)生變化,。當(dāng)

都發(fā)生變化,。當(dāng) 時(shí),,電抗

時(shí),,電抗 ,電路的入端阻抗

,電路的入端阻抗 為純電阻,。此時(shí)電壓和電流同相位,,電路產(chǎn)生諧振現(xiàn)象。此種電路因?yàn)?/span>L與C是相串聯(lián)的,,所以稱為串聯(lián)諧振,。電路發(fā)生串聯(lián)諧振的條件為電抗值等于零,即

為純電阻,。此時(shí)電壓和電流同相位,,電路產(chǎn)生諧振現(xiàn)象。此種電路因?yàn)?/span>L與C是相串聯(lián)的,,所以稱為串聯(lián)諧振,。電路發(fā)生串聯(lián)諧振的條件為電抗值等于零,即

或

或

電路發(fā)生諧振時(shí)的角頻率稱為諧振角頻率,,用 來表示

來表示

(2)

(2)

電路諧振頻率為

(3)

(3)

電路發(fā)生諧振時(shí),,電路的總電抗 ,但感抗

,但感抗 與容抗

與容抗 本身并不為零,,它們的值為

本身并不為零,,它們的值為

(4)

(4)

稱為諧振電路的特性阻抗,,其單位為

稱為諧振電路的特性阻抗,,其單位為 ,。

,。

電路諧振時(shí),,電感電壓等于電容電壓,,且二者相位差為180°,故互相抵消,。

電阻上的壓降等于外加電壓。電壓與電流的相量圖如圖1b所示,。

串聯(lián)諧振時(shí),,電路儲(chǔ)存于電感中的磁場能與儲(chǔ)存于電容元件中的電場能之間進(jìn)行能量交換。設(shè)外施電壓為 ,,則在串聯(lián)諧振時(shí),,電路中電感電流和電容電壓分別為

,,則在串聯(lián)諧振時(shí),,電路中電感電流和電容電壓分別為

此時(shí)電感儲(chǔ)存的磁場能為:

電容儲(chǔ)存的電場能量為:

由 可得:

可得:

可見磁場能與電場能的最大值是相等的。電磁場能量的總和

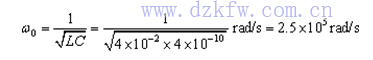

例1 圖3所示電路,,已知 ,,

,, ,,

,, ,求該串聯(lián)電路的諧振頻率

,求該串聯(lián)電路的諧振頻率 ,,特性阻抗

,,特性阻抗 和電路的品質(zhì)因數(shù)Q,。

和電路的品質(zhì)因數(shù)Q,。

圖3

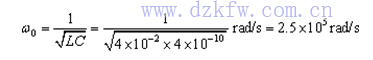

解:電路的諧振角頻率

諧振頻率

特性阻抗

品質(zhì)因數(shù)

除了RLC串聯(lián)諧振電路外,并聯(lián)RLC諧振電路也被廣泛采用,。RLC并聯(lián)諧振電路如圖4所示,。它的入端導(dǎo)納為

由此式可見,當(dāng)選擇 ,,L或C的參數(shù)使之滿足并聯(lián)電路的感納與容納相等,,即

,,L或C的參數(shù)使之滿足并聯(lián)電路的感納與容納相等,,即 ,

,

圖4

則此時(shí)導(dǎo)納的虛部為零,,導(dǎo)納成為純電導(dǎo) ,,電路入端電壓

,,電路入端電壓 與電流

與電流 相位相同。這種情況就稱為RLC并聯(lián)電路諧振,。由上述可知,,并聯(lián)諧振的角頻率為

相位相同。這種情況就稱為RLC并聯(lián)電路諧振,。由上述可知,,并聯(lián)諧振的角頻率為

并聯(lián)諧振的條件是感納與容納相等 ,或

,或 ,。此時(shí)電路入端電流

,。此時(shí)電路入端電流

各元件上電流分別為

各電流相量如圖4-1-4所示,。并聯(lián)諧振時(shí),若外加電壓不變,,則諧振時(shí)流入的電流最小,,此電流等于電阻上流過的電流。電感上無功電流 的幅值與電容上無功電流

的幅值與電容上無功電流 的幅值相等,,相位差為

的幅值相等,,相位差為 ,,二者互相抵消,故并聯(lián)諧振又被稱為電流諧振,。若并聯(lián)電路中沒有電導(dǎo)G的支路,,則諧振時(shí)入端導(dǎo)納

,,二者互相抵消,故并聯(lián)諧振又被稱為電流諧振,。若并聯(lián)電路中沒有電導(dǎo)G的支路,,則諧振時(shí)入端導(dǎo)納 ,其等效阻抗

,其等效阻抗 ,,因此由LC并聯(lián)而成的電路在發(fā)生諧振時(shí),,其入端電流

,,因此由LC并聯(lián)而成的電路在發(fā)生諧振時(shí),,其入端電流 。

。

并聯(lián)諧振電路的品質(zhì)因數(shù)定義為電路感納 (或容納

(或容納 )與電導(dǎo)

)與電導(dǎo) 之比,,即

之比,,即

品質(zhì)因數(shù)也等于電感電流的幅值(或電容電流的幅值)與流過電阻的電流幅值之比

您好, 歡迎來到化工儀器網(wǎng)

您好, 歡迎來到化工儀器網(wǎng)