在芯片制造過程中,,芯片引腳扮演著連接內(nèi)部電路與外部電路的重要角色,相當(dāng)于芯片的接口,。然而在芯片制造過程中,,如果引腳出現(xiàn)缺失、破損,、偏斜或不平整,,容易導(dǎo)致后續(xù)貼片焊接時出現(xiàn)虛焊、虛接或漏接的問題,,進而影響芯片的可靠性,。

芯片引腳缺陷檢測通常涉及測量和評估多個指標(biāo),如檢測引腳外觀,、測量引腳寬度,、高度差等,通過綜合評估這些參數(shù),,能夠及時發(fā)現(xiàn)潛在的問題并提供預(yù)警,,以確保芯片制造的質(zhì)量和可靠性。

如何在芯片快速傳輸?shù)倪^程中,,高效準(zhǔn)確地對引腳缺陷進行非接觸式測量分析,,是芯片廠商亟待解決的問題。

SOPTOPMS測量顯微鏡結(jié)合了金相顯微鏡的高倍觀察能力,,和影像測量儀的X,、Y、Z軸表面尺寸測量功能,,采用0.1μm高精度3軸測量系統(tǒng),,可精確監(jiān)控引腳之間的間距、高度,、長度等,,驗證抽檢樣品是否符合設(shè)計要求。

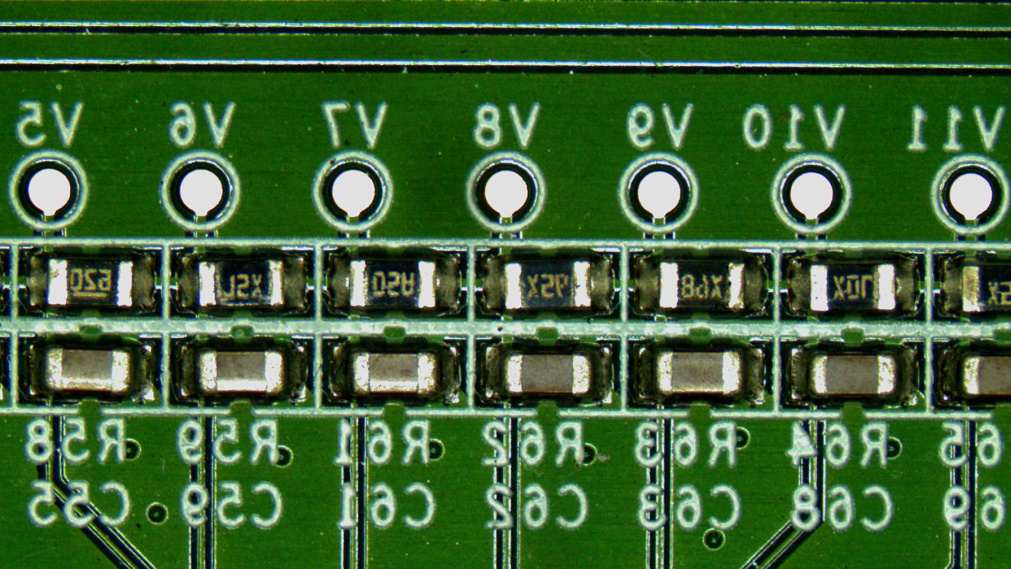

引腳外觀和形狀

檢查引腳的外觀,,確保沒有損壞,、變形或其他表面缺陷,,這些問題可能會影響引腳的功能性和可靠性。

引腳位置和對齊

測量引腳位置和對齊,,評估引腳之間的間距和間隙,,確保它們符合設(shè)計規(guī)范,不正確的位置或?qū)R可能導(dǎo)致連接不良或損壞,。

焊點完整性

評估焊點的完整性,,包括焊料的均勻性、潤濕性和穩(wěn)定性,。良好的焊點確保引腳與主板或其他元件之間可靠連接,。

隨著先進工藝集成度和電路復(fù)雜度日益攀升,芯片引腳尺寸不斷減小,,制造工序逐漸復(fù)雜,。更具競爭力的光學(xué)量測設(shè)備才能更好地迎合檢測市場需求。

未來,,SOPTOP也將不斷致力于提高檢測效率和精度,,優(yōu)化圖像質(zhì)量,為半導(dǎo)體檢測賦能,。

(空格分隔,最多3個,單個標(biāo)簽最多10個字符)

立即詢價

您提交后,,專屬客服將第一時間為您服務(wù)