目錄

收起

一. DDR標(biāo)準(zhǔn)發(fā)展和 DDR5簡(jiǎn)介

DDR是什么?

DDR內(nèi)存原理

DDR工作原理

存儲(chǔ)器分類

如何計(jì)算DDR帶寬,?

SDRAM和DDR區(qū)別是什么?

DDR5和DDR4的區(qū)別

DDR發(fā)展歷程

DDR4和DDR5的性能差距?

2.1.1 速率的提升

2.1.2 電壓的降低

2.1.3 DIMM新電源架構(gòu)

2.1.4 DIMM通道架構(gòu)

2.1.5 更長(zhǎng)的突發(fā)長(zhǎng)度

2.1.6 更大容量的 DRAM

DDR5主要特點(diǎn)

DDR5測(cè)試方案

二. 發(fā)送端測(cè)試方法

首先來看 UI定義 - UI是啥?

眼圖測(cè)試

如何計(jì)算總體抖動(dòng)?

三,、DDR5測(cè)試新方法

3.2 接收端RX測(cè)試挑戰(zhàn)

DDR,、LPDDR的協(xié)議解碼測(cè)試總結(jié)

內(nèi)存(DRAM-Random Access Memory)作為當(dāng)代數(shù)字系統(tǒng)最主要的核心部件之一,從各種終端設(shè)備到核心層數(shù)據(jù)處理 和存儲(chǔ)設(shè)備,,從各種消費(fèi)類電子設(shè)備到社會(huì)各行業(yè)專用設(shè)備,,是各種級(jí)別的 CPU 進(jìn)行數(shù)據(jù)處理運(yùn)算和緩存的buke或缺的周轉(zhuǎn)“倉庫",一個(gè)強(qiáng)大的核心處理單元也必須配備一個(gè)高速運(yùn)轉(zhuǎn)的寬通路的數(shù)據(jù)訪問和存儲(chǔ)單元,。近 20 多年來,,DRAM也快速地從 20 世紀(jì)末期的 SDRAM 發(fā)展到 21 世紀(jì) DDR RAM。在 21 世紀(jì)的qian10 年,,DDR標(biāo)準(zhǔn)主要是個(gè)人信息處理終端的代表設(shè)備----PC 和個(gè)人工作站類驅(qū)動(dòng),,快速從 DDR1 演進(jìn)到 DDR3。而近 10 年來,,進(jìn)入移動(dòng)互聯(lián)時(shí)代后海量數(shù)據(jù)爆發(fā),,AI 和深度學(xué)習(xí)以及 5G驅(qū)動(dòng),,在個(gè)人信息終端上基本可以勝任的 DDR4標(biāo)準(zhǔn),明顯顯得力不從心,。今天 DDR5正在昂首闊步地配合以 PCIE5.0 32Gbps 為代表的第5代高速 I/O 數(shù)據(jù)傳輸走向最終的市場(chǎng)化,。

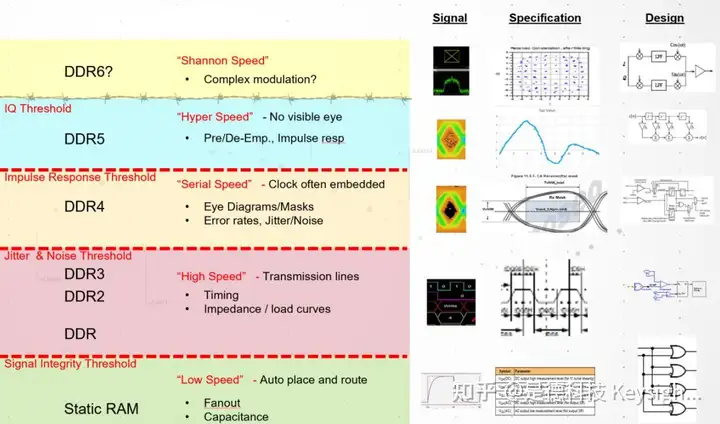

下圖展示的是內(nèi)存 RAM 20多年來的發(fā)展和信號(hào)特點(diǎn)以及設(shè)計(jì)演進(jìn),。

圖 1 DDR標(biāo)準(zhǔn)發(fā)展和信號(hào)特點(diǎn)演進(jìn)

一些DDR基本概念

DDR的全拼是Double Data Rate SDRAM雙倍數(shù)據(jù)速率同步動(dòng)態(tài)隨機(jī)存取內(nèi)存, 主要用在電腦的內(nèi)存,。DDR的特點(diǎn)就是走線數(shù)量多,速度快,,操作復(fù)雜,,給測(cè)試和分析帶來了很大的挑戰(zhàn)。

目前DDR技術(shù)已經(jīng)發(fā)展到了DDR5,,性能更高,,功耗更低,存儲(chǔ)密度更高,,芯片容量大幅提升,,他的數(shù)據(jù)速率在3200-6400MT/s。

DDR本質(zhì)上不需要提高時(shí)鐘頻率就能加倍提高SDRAM的速度,,它允許在時(shí)鐘的上升沿和下降沿讀出數(shù)據(jù),,因而其速度是標(biāo)準(zhǔn)SDRAM的兩倍,至于地址與控制信號(hào)則與傳統(tǒng)SDRAM相同,,仍在時(shí)鐘上升沿進(jìn)行數(shù)據(jù)判斷,。

DDR核心技術(shù)點(diǎn)就在于雙沿傳輸和預(yù)取Prefetch.

DDR的頻率包括核心頻率,時(shí)鐘頻率和數(shù)據(jù)傳輸頻率,。核心頻率就是內(nèi)存的工作頻率,;DDR1內(nèi)存的核心頻率是和時(shí)鐘頻率相同的,到了DDR2和DDR3時(shí)才有了時(shí)鐘頻率的概念,,就是將核心頻率通過倍頻技術(shù)得到的一個(gè)頻率,。數(shù)據(jù)傳輸頻率就是傳輸數(shù)據(jù)的頻率。

推薦閱讀:

DDR 存儲(chǔ)器概述,、開發(fā)周期和挑戰(zhàn)

“由于改進(jìn)的制造工藝降低了成本,,現(xiàn)在選擇的技術(shù)是 DDR SDRAM,是雙倍數(shù)據(jù)速率同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器的縮寫,。"

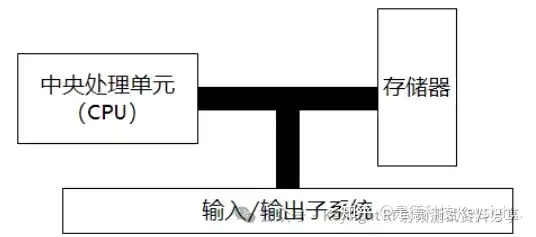

計(jì)算機(jī)組成

計(jì)算機(jī)組成結(jié)構(gòu) (Computer Architecture)是計(jì)算機(jī)系統(tǒng)的核心,,它定義了計(jì)算機(jī)的基本工作原理和設(shè)計(jì)模式。計(jì)算機(jī)的組成可以分成以下3大類:中央處理器(CPU),、存儲(chǔ)器和輸入/輸出子系統(tǒng),。

中央處理器 (CPU)

CPU用于數(shù)據(jù)的運(yùn)算,在大部分的體系結(jié)合中,,它有3個(gè)組成部分:算數(shù)運(yùn)算單元 (ALU),、控制單元,、奇存器組。

控制單元 (Control Unit):負(fù)責(zé)指揮整個(gè)計(jì)算機(jī)系統(tǒng)的操作,,解釋并執(zhí)行指令,,控制其他硬件的工作。

算術(shù)邏輯單元 (ALU):執(zhí)行所有算術(shù)運(yùn)算(如加減乘除)和邏輯運(yùn)算(如與,、或,、非等),是計(jì)算機(jī)執(zhí)行指令的核心部分,。

寄存器 (Registers):這是CPU中用于存儲(chǔ)數(shù)據(jù)的高速行儲(chǔ)器,,用來臨時(shí)存放指令、數(shù)據(jù)和操作結(jié)果,。

半導(dǎo)體存儲(chǔ)器

隨著科技的發(fā)展,,半導(dǎo)體存儲(chǔ)器成為了現(xiàn)代計(jì)算機(jī)存儲(chǔ)器的主流,分為兩類主要類型:

靜態(tài)隨機(jī)存儲(chǔ)器 (SRAM):SRAN利用晶體管存儲(chǔ)數(shù)據(jù),,速度非??欤總€(gè)比特需要更多的晶體管,,導(dǎo)致成本高,,密度低。主要應(yīng)用在需要高速綏存的場(chǎng)景,,如CPU的緩存 (L1,、 L2、 L3)

動(dòng)態(tài)隨機(jī)存儲(chǔ)器 (DRAM):DRAM利用電容存儲(chǔ)數(shù)據(jù),,電容逐漸放電,,因此需要不斷刷新來維持?jǐn)?shù)據(jù)存儲(chǔ)。相對(duì)于SRAM,DRAM的存儲(chǔ)密度更高,,成本較低,,因此廣泛用于主內(nèi)存 (RAM)。隨看集成電路制造技術(shù)的進(jìn)步,,DRAN容量和性能持續(xù)提升,。

現(xiàn)代內(nèi)存技術(shù)

DDR(雙倍數(shù)據(jù)速率)內(nèi)存:從DDR到如今的DDR5,隨看數(shù)據(jù)傳輸速度和功耗的改進(jìn),,DDR系列內(nèi)存成為計(jì)算機(jī)和服務(wù)器的主流內(nèi)存,。DDR技術(shù)從2000年開始引入,持續(xù)更新,,DDR5的帶完和容量比早期版本有了大幅提升,。

閃存 (Flash Memory):閃存 (Flash Memory)是一種長(zhǎng)壽命的非易失性的存儲(chǔ)器,數(shù)據(jù)刪除不是以單個(gè)的字節(jié)為單位而是以固定的區(qū)塊為單位,。閃存是電子可擦除只讀存儲(chǔ)器(EEPROM) 的變種,,閃存與EEPROM不同的是,,EEPROM能在字節(jié)水平上進(jìn)行刪除和重寫而不是整個(gè)芯片擦寫,而閃存的大部分芯片需要塊擦除,。由于其斷電時(shí)仍能保存數(shù)據(jù),,閃存通常被用來保存設(shè)置信息,如在電腦的B1OS(基本程序),、PDA(個(gè)人數(shù)字助理),、數(shù)碼相機(jī)中保存資料等。

LPDDR(低功耗DDR):隨看移動(dòng)設(shè)備的普及,,低功耗內(nèi)存技術(shù)成為了關(guān)鍵,,LPDDR(低功耗雙倍數(shù)據(jù)速率)內(nèi)存在手機(jī),、平板等設(shè)備上應(yīng)用廣泛,,從LPDDR1發(fā)展到LPDDR5,強(qiáng)調(diào)功耗和性能之間的平衡,。

HBM (High Bandwidth Memory,,高帶亮內(nèi)存): HBM是一種高性能DRAM,具有更高的帶完和更低的功耗,,主要用于圖形處理器(GPU) 和高性能計(jì)算 (HPC)領(lǐng)域,。HBM通過垂直堆愛的方式來提升存儲(chǔ)密度和傳輸速度,減少了延遲和能耗,。

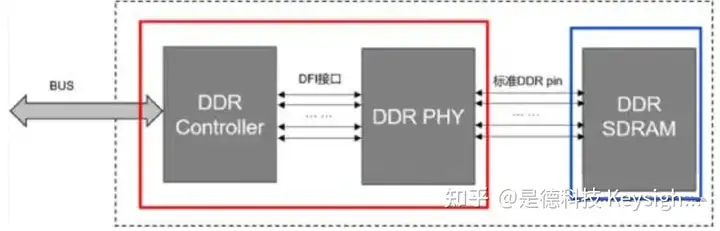

基本DDR subsystem架構(gòu)圖:DDRC +DDRphy +SDRAM顆粒,,DDR IP一般包括DDR Controller和DDR PHY,內(nèi)部涉及的內(nèi)容包括但不限于以下幾個(gè)方面:數(shù)據(jù)保序,、仲裁,、zuiyou調(diào)度、協(xié)議狀態(tài)機(jī)設(shè)計(jì),、防餓死機(jī)制,、bypass通路、快速切頻,、DDR training

當(dāng)時(shí)鐘脈沖達(dá)到一定頻率時(shí),,DDR存儲(chǔ)器才開始工作,此后發(fā)生的就是“讀-存-讀"的過程,。在此過程中,,器件芯片會(huì)從主在取數(shù)據(jù),然后與入數(shù)據(jù)在儲(chǔ)區(qū),。當(dāng)寫入操作完成后,,再從存儲(chǔ)區(qū)中取出數(shù)據(jù),並將其傳輸?shù)教幚砥髦?,然后根?jù)需要將數(shù)據(jù)處理,,再把最終結(jié)果返回到主存,。

DDR 的雙倍數(shù)據(jù)傳輸率其實(shí)就是每個(gè)時(shí)鐘周期內(nèi)讀寫一次數(shù)據(jù),即DDR芯片可以在每個(gè)時(shí)鐘周期內(nèi)分別完成“讀-存"和“存-讀"操作,,從而提高存儲(chǔ)器的傳輸效率,。

DDR內(nèi)存通過雙倍數(shù)據(jù)速率的傳輸方式,結(jié)合多通道傳輸和數(shù)據(jù)校驗(yàn)等技術(shù),,提高了數(shù)據(jù)傳輸效率和可靠性,。這使得 DDR 成為了計(jì)算機(jī)內(nèi)存的主流技術(shù)。

內(nèi)存芯片 - DDR內(nèi)存模塊中包含多個(gè)內(nèi)存芯片,,每個(gè)芯片有自己的存儲(chǔ)單元,。每個(gè)存儲(chǔ)單元都有一個(gè)地址,用于在讀取或?qū)懭霐?shù)據(jù)時(shí)進(jìn)行尋址,。

數(shù)據(jù)總線 - DDR內(nèi)存模塊連接到計(jì)算機(jī)的內(nèi)存控制器,,通過數(shù)據(jù)總線進(jìn)行數(shù)據(jù)傳輸。數(shù)據(jù)總線可以同時(shí)傳輸多個(gè)數(shù)據(jù)位,,例如 64 位或 128位,。

時(shí)鐘信號(hào) - DDR內(nèi)存模塊通過時(shí)鐘信號(hào)進(jìn)行同步操作。時(shí)鐘信號(hào)用來控制數(shù)據(jù)的傳輸速率,,每個(gè)時(shí)鐘周期內(nèi)有一個(gè)上升沿和一個(gè)下降沿,。上升沿時(shí),數(shù)據(jù)從內(nèi)存芯片傳輸?shù)綌?shù)據(jù)總線,;下降沿時(shí),,數(shù)據(jù)從數(shù)據(jù)總線傳輸?shù)絻?nèi)存芯片。

預(yù)充電 - 在開始傳輸數(shù)據(jù)之前,,DDR內(nèi)存模塊會(huì)先進(jìn)行預(yù)充電操作,。預(yù)充電是將存儲(chǔ)單元中的電荷恢復(fù)到初始狀態(tài),以確保接下來的數(shù)據(jù)傳輸是準(zhǔn)確的,。

數(shù)據(jù)傳輸 - DDR 采用了多通道的數(shù)據(jù)傳輸方式,,即同時(shí)傳輸多個(gè)數(shù)據(jù)位。這樣可以在每個(gè)時(shí)鐘周期內(nèi)傳輸更多的數(shù)據(jù),。

存儲(chǔ)器分為內(nèi)部存儲(chǔ)器(內(nèi)存),,外部存儲(chǔ)器(外存),緩沖存儲(chǔ)器(緩存)以及閃存這幾個(gè)大類,。

內(nèi)存也稱為主存儲(chǔ)器,,位于系統(tǒng)主機(jī)板上,可以同CPU直接進(jìn)行信息交換,。其主要特點(diǎn)是:運(yùn)行速度快,,容量小。

外存也稱為輔助存儲(chǔ)器,不能與CPU之間直接進(jìn)行信息交換,。其主要特點(diǎn)是:存取速度相對(duì)內(nèi)存要慢得多,,存儲(chǔ)容量大。

內(nèi)存與外存本質(zhì)區(qū)別是,,一個(gè)是內(nèi)部運(yùn)行提供緩存和處理的功能,,也可以理解為協(xié)同處理的通道;而外存主要是針對(duì)儲(chǔ)存文件、圖片,、視頻,、文字等信息的載體,也可以理解為儲(chǔ)存空間,。緩存就是數(shù)據(jù)交換的緩沖區(qū) (稱作Cache),,當(dāng)某一硬件要讀取數(shù)據(jù)時(shí),會(huì)首先從緩存中查找需要的數(shù)據(jù),,如果找到了則直接執(zhí)行,,找不到的話則從內(nèi)存中找。由于緩存的運(yùn)行速度比內(nèi)存快得多,,故緩存的作用就是幫助硬件更快地運(yùn)行,。

閃存 (Flash Memory)是一種長(zhǎng)壽命的非易失性的存儲(chǔ)器,,數(shù)據(jù)刪除不是以單個(gè)的字節(jié)為單位而是以固定的區(qū)塊為單位,。閃存是電子可擦除只讀存儲(chǔ)器(EEPROM) 的變種,閃存與EEPROM不同的是,,EEPROM能在字節(jié)水平上進(jìn)行刪除和重寫而不是整個(gè)芯片擦寫,,而閃存的大部分芯片需要塊擦除。由于其斷電時(shí)仍能保存數(shù)據(jù),,閃存通常被用來保存設(shè)置信息,,如在電腦的B1OS(基本程序)、PDA(個(gè)人數(shù)字助理),、數(shù)碼相機(jī)中保存資料等,。

內(nèi)存帶寬計(jì)算公式1:

帶寬=內(nèi)存核心頻率×倍增系數(shù)×(內(nèi)存總線位數(shù)/8)

內(nèi)存帶寬計(jì)算公式2:

帶寬=標(biāo)稱頻率×線寬 ÷ 8

DDR=雙倍速率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,,是內(nèi)存的其中一種,。DDR取消了主板與內(nèi)存兩個(gè)存儲(chǔ)周期之間的時(shí)間間隔,每隔2個(gè)時(shí)鐘脈沖周期傳輸一次數(shù)據(jù),,大大地縮短了存取時(shí)間,使存取速度提高百分之三十,。

SDRAM是 "Synchronous Dynamic random access memory"的縮寫,意思是“同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器",,就是我們平時(shí)所說的“同步內(nèi)存",。從理論上說,SDRAM與CPU頻率同步,,共享一個(gè)時(shí)鐘周期,。SDRAM內(nèi)含兩個(gè)交錯(cuò)的存儲(chǔ)陣列,,當(dāng)CPU從一個(gè)存儲(chǔ)陣列訪問數(shù)據(jù)的同時(shí),另一個(gè)已準(zhǔn)備好讀寫數(shù)據(jù),,通過兩個(gè)存儲(chǔ)陣列的緊密切換,,讀取效率得到成倍提高。

DDR是SDRAM的更新?lián)Q代產(chǎn)品,,采用5伏工作電壓,,允許在時(shí)鐘脈沖的上升沿和下降沿傳輸數(shù)據(jù),這樣不需要提高時(shí)鐘的頻率就能加倍提高SDRAM的速度,,并具有比SDRAM多一倍的傳輸速率和內(nèi)存帶寬,。

DDR誤碼率測(cè)量

DDR(DDR1)-DDR SDRAM 于 2000 年推出,與其前身 SDR SDRAM(單速率 SDRAM)相比有了顯著的改進(jìn),。與 SDR SDRAM 相比,,DDR1 的數(shù)據(jù)傳輸速率提高了一倍,從而實(shí)現(xiàn)了更快的內(nèi)存訪問速度并提高了系統(tǒng)性能,。DDR1 模塊最初提供的數(shù)據(jù)傳輸速率范圍為 200 MT/s 至 400 MT/s(每秒兆次傳輸),。DDR1 內(nèi)存通常用于臺(tái)式計(jì)算機(jī)、筆記本電腦和早期的服務(wù)器系統(tǒng),。

DDR2 - DDR2 SDRAM 于 2003 年推出,,在 DDR1 的基礎(chǔ)上進(jìn)一步提高了速度和效率。與 DDR1 相比,,DDR2 的預(yù)取緩沖區(qū)大小增加了一倍,,從而可以提高數(shù)據(jù)吞吐量。DDR2 模塊最初提供的數(shù)據(jù)傳輸速率范圍為 400 MT/s 至 800 MT/s,。DDR2 內(nèi)存在中端到gaoduan計(jì)算系統(tǒng)中得到廣泛應(yīng)用,,與 DDR1 相比,其性能和能效更高,。

DDR3 - 2007 年發(fā)布的 DDR3 SDRAM 代表著內(nèi)存技術(shù)的又一次重大進(jìn)步,。與 DDR2 相比,DDR3 進(jìn)一步提高了數(shù)據(jù)傳輸速率,,同時(shí)降低了功耗,。DDR3 模塊最初支持的數(shù)據(jù)傳輸速率從 800 MT/s 到 1600 MT/s,后來的速度最高可達(dá) 2133 MT/s,。DDR3 內(nèi)存成為主流計(jì)算系統(tǒng)的標(biāo)準(zhǔn),,在性能、能效和價(jià)格之間實(shí)現(xiàn)了平衡,。

作為當(dāng)前市場(chǎng)主流的 DDR4標(biāo)準(zhǔn)和業(yè)界正在集中攻關(guān)的 DDR5標(biāo)準(zhǔn),,對(duì)比有何差異呢?

如下表所列,從芯片開發(fā)到電路系統(tǒng)設(shè)計(jì)角度來看相比,DDR5 為了實(shí)現(xiàn)更高帶寬和吞吐量進(jìn)一步提升讀寫速率和改變通道架構(gòu)以及猝發(fā)讀寫長(zhǎng)度,,目前規(guī)劃的最高速率達(dá) 8400M T/s,。

為了實(shí)現(xiàn)更低功耗和電源管理 I/O 電壓降到 1.1V,并在 DIMM 條上完成電源管理工作以實(shí)現(xiàn)更高 的電源效率(主要是縮短電源傳輸路徑以降低損耗和減小潛在的干擾),。為了提高數(shù)據(jù)帶寬,,不僅 提升速率同時(shí)采用雙通道架構(gòu),提升讀寫效率,,采用雙通道 32 data + 8 ECC,,Burst Length 也從 4/8 提高到 8/16,最后還支持更高容量的 DRAM 器件,,從 DDR4 16 Gb 加倍到 32 Gb,。總之,,DDR5 作為業(yè)界備受期望的第 5 代 I/O 的內(nèi)部數(shù)據(jù)共享和傳輸標(biāo)準(zhǔn)將與 PCI Express 5.0 乃至 6.0 等高速接口標(biāo)準(zhǔn)一起重塑 iABC 時(shí)代的大數(shù)據(jù)流的高速公路,。

表 1 DDR4 和 DDR5 比較(源自 Rambus)

近年來,內(nèi)存與CPU性能發(fā)展之間的剪刀差越來越大,,對(duì)內(nèi)存帶寬的需求日益迫切,。DDR4在1.6GHz的時(shí)鐘頻率下最高可達(dá) 3.2 GT/s的傳輸速率,最初的 DDR5則將帶寬提高了 50%,,達(dá)到 4.8 GT/s傳輸速率,。DDR5 內(nèi)存的數(shù)據(jù)傳輸速率最終將會(huì)達(dá)到 8.4 GT/s。

降低工作電壓(VDD),,有助于抵消高速運(yùn)行帶來的功耗增加,。在 DDR5 DRAM 中,寄存時(shí)鐘驅(qū)動(dòng)器 (RCD) 電壓從 1.2 V 降至 1.1 V,。命令/地址 (CA) 信號(hào)從 SSTL 變?yōu)?PODL,其優(yōu)點(diǎn)是當(dāng)引腳處于高電平狀態(tài)時(shí)不會(huì)消耗靜態(tài)功率,。

使用 DDR5 DIMM 時(shí),,電源管理將從主板轉(zhuǎn)移到 DIMM 本身。DDR5 DIMM 將在 DIMM 上安裝一個(gè) 12 V 電源管理集成電路(PMIC),,使系統(tǒng)電源負(fù)載的顆粒度更細(xì),。PMIC 分配1.1 V VDD 電源,通過更好地在 DIMM 上控制電源,,有助于改善信號(hào)完整性和噪音,。

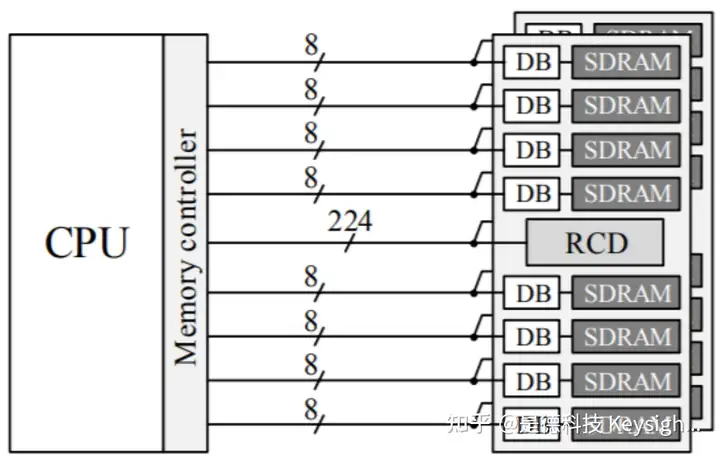

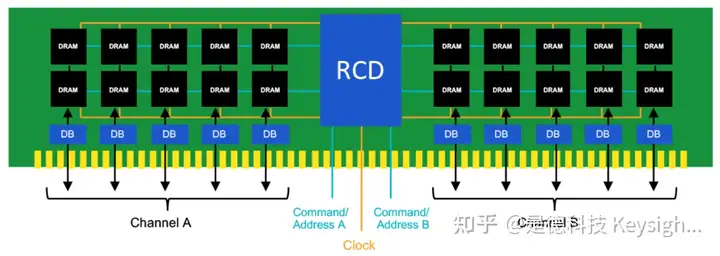

DDR4 DIMM 具有 72 位總線,由 64 個(gè)數(shù)據(jù)位和 8 個(gè) ECC 位組成,。在 DDR5 中,,每個(gè) DIMM 都有兩個(gè)通道。每個(gè)通道寬 40 位,32 個(gè)數(shù)據(jù)位和 8 個(gè) ECC 位,。雖然數(shù)據(jù)寬度相同(共 64 位),,但兩個(gè)較小的獨(dú)立通道提高了內(nèi)存訪問效率。因此,,使用 DDR5 不僅能提高速度,,還能通過更高的效率放大更高的傳輸速率。

圖 2 DDR5總線架構(gòu)和標(biāo)準(zhǔn)DDR5 RDIMM 內(nèi)存條

DDR4 的突發(fā)長(zhǎng)度為4或者8,。對(duì)于 DDR5,,突發(fā)長(zhǎng)度將擴(kuò)展到8和16,以增加突發(fā)有效載荷,。突發(fā)長(zhǎng)度為16(BL16),,允許單個(gè)突發(fā)訪問 64 字節(jié)的數(shù)據(jù),這是典型的 CPU 高速緩存行大小,。它只需使用兩個(gè)獨(dú)立通道中的一個(gè)通道即可實(shí)現(xiàn)這一功能,。這極大地提高了并發(fā)性,并且通過兩個(gè)通道提高了內(nèi)存效率,。

DDR4 在單芯片封裝(SDP)中的最大容量為16 Gb DRAM,。而DDR5的單芯片封裝最大容量可達(dá)64 Gb,組建的DIMM 容量則翻了兩番,,達(dá)到驚人的 256 GB,。

應(yīng)用指南

無矢量測(cè)試:nanoVTEP 與 VTEP

本應(yīng)用指南總結(jié)了在客戶現(xiàn)場(chǎng)進(jìn)行的無矢量測(cè)試增強(qiáng)型探針 (VTEP) 早期測(cè)試的一些結(jié)果。

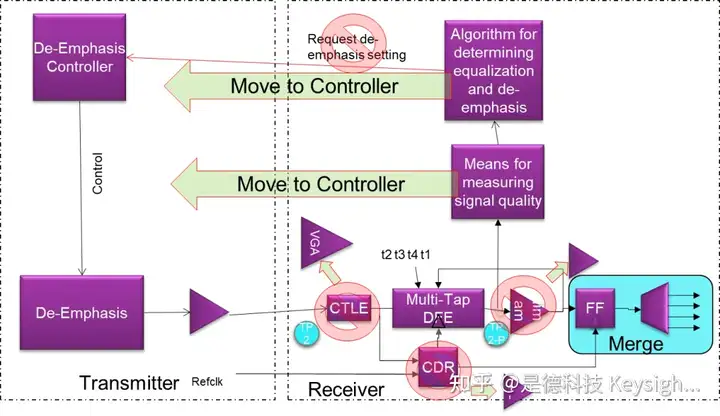

從物理層信號(hào)角度來看,,DDR5主要有如下特點(diǎn):

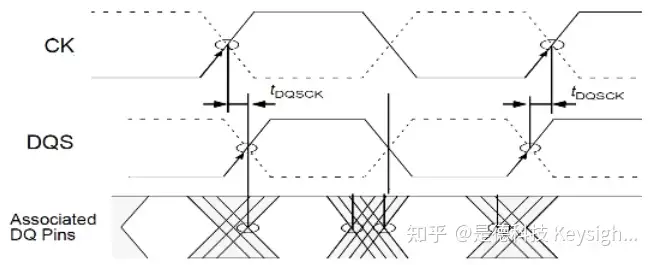

1.采用分離式全速率時(shí)鐘,,對(duì)應(yīng) 6400M T/s 頻率最高達(dá) 3.2GHz。

時(shí)鐘控制命令信號(hào),選通信號(hào)控制數(shù)據(jù),如上圖示,。

對(duì)時(shí)鐘信號(hào)抖動(dòng)的要求更加嚴(yán)格,,對(duì)各 種命令信號(hào)與數(shù)據(jù)和地址信號(hào)的時(shí)序要求也更高。

2.更寬的總線,,單端信號(hào),,從 RCD(Registering Clock Drivers)芯片來看采用 Multi-Drop 架構(gòu)。

基于今天更寬的總線需求,,在一塊刀片服務(wù)器上可能支持 1000+個(gè)并行數(shù)據(jù)通道,。且由于 繼續(xù)采用單端信號(hào)且速率倍增,傳統(tǒng)只在串行差分電路上考慮的損耗問題也開始困擾 DDR5,。因此 在 DDR5設(shè)計(jì)和驗(yàn)證測(cè)試上,,不僅需要考慮傳統(tǒng)的串?dāng)_問題還增加了對(duì)電路損耗問題的考慮。

應(yīng)用指南

DDR5走線的正確受控阻抗是多少,?

本文檔檢查了 DDR器件供應(yīng)商提出的受控阻抗建議,,將這些建議與制造電路板上的阻抗進(jìn)行比較,,并提供設(shè)計(jì)建議。 鑒于缺乏可用的 DDR5設(shè)計(jì),,本案例研究重點(diǎn)關(guān)注現(xiàn)有開源 DDR4設(shè)計(jì)的阻抗,。對(duì)供應(yīng)商建議的最大和最小阻抗范圍以及已制造的 DDR設(shè)計(jì)中的阻抗進(jìn)行了比較。 制造的開源板均具有在建議范圍內(nèi)的 DDR控制阻抗,。

3.雙向復(fù)用的數(shù)據(jù)總線,,讀寫數(shù)據(jù)分時(shí)復(fù)用鏈路。 囿于有限的鏈路通道和布板空間等資源讀寫操作繼續(xù)采用共享總線,,因此需要分時(shí)操作,。

從驗(yàn)證測(cè)試角度來看也需要分別對(duì)讀和寫信號(hào)進(jìn)行分離以檢查其是否滿足規(guī)范。

圖 4 DDR5 讀寫共享總線

4.猝發(fā) DQS 和 DQ 信號(hào)在更高速率的背景下在有限帶寬的鏈路傳輸時(shí)帶來更多 ISI 效應(yīng)問題,。

在 DQS 讀寫前導(dǎo)位,,猝發(fā)第一個(gè) bit 等等均有不同的效應(yīng)和表現(xiàn)。此外考慮到存儲(chǔ)電路在設(shè)計(jì)上不同于串行電路存在較多的阻抗不匹配,,因此反射問題或干擾帶來的 ISI 也會(huì)更嚴(yán)重,。

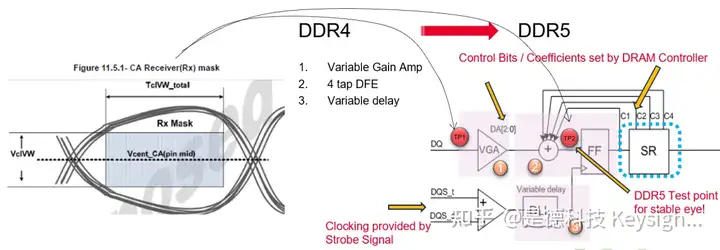

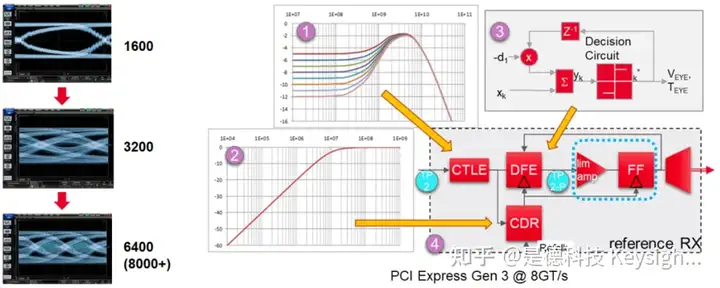

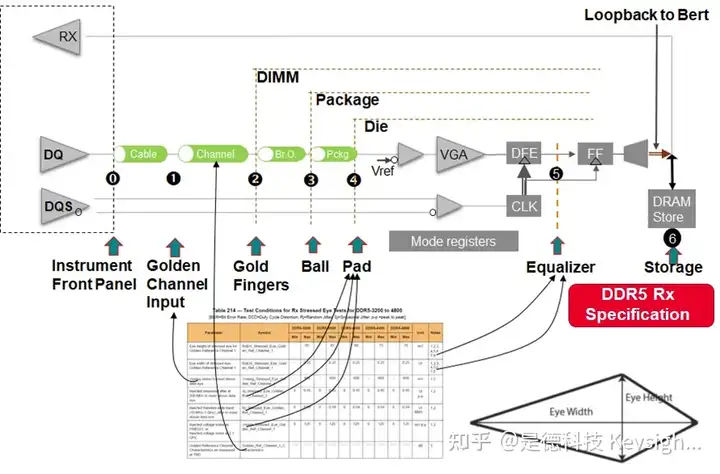

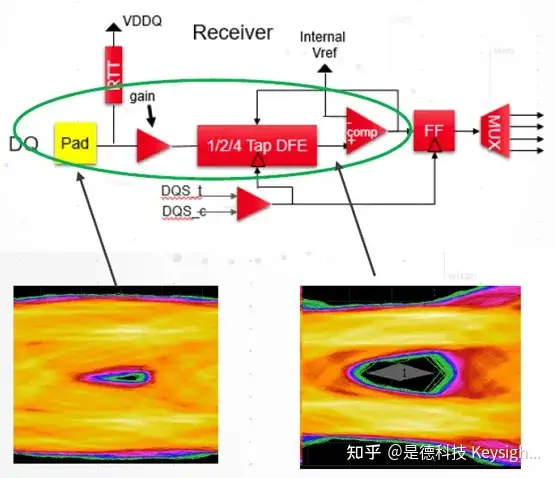

圖 5 DDR5 在接收端采用更多的類似高速串行總線的信號(hào)處理

因此在接收側(cè)速率大于 3600M T/s 時(shí)采用類似高速串行電路和標(biāo)準(zhǔn)總線中已經(jīng)成熟的 DFE 均衡技術(shù),可變?cè)鲆娣糯?VGA)則通過 MR 寄存器配置,,以補(bǔ)償在更高速率傳輸時(shí)鏈路上的損耗,。 DDR4標(biāo)準(zhǔn)采用的 CTLE 作為常用的線性均衡放大,雖然簡(jiǎn)單易實(shí)現(xiàn)但是其放大噪聲的副產(chǎn)品也更 為常見,,考慮到 DDR5總線里的反射噪聲比沒有采用,。另外考慮到并行總線的串?dāng)_和反射等各信 號(hào)抖動(dòng)的定義和分析也會(huì)隨之變化。

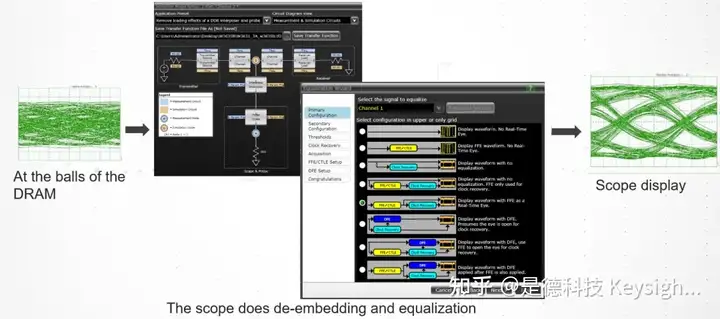

從測(cè)試角度來看,,示波器是無法得到 TP2點(diǎn)即均衡后的信號(hào)的,,而僅能得到 TP1點(diǎn)的信 號(hào),然后通過集成在示波器上的分析軟件里的均衡算法對(duì)信號(hào)進(jìn)行均衡處理以得到張開的眼圖,。 眼圖分析的參考時(shí)鐘則來自基于時(shí)鐘信號(hào)的 DQS 信號(hào),。另外眼圖測(cè)試也從以往僅對(duì) DQ 進(jìn)行擴(kuò)展 到包括 CMD/ADDR總線。

以上我們介紹了 DDR5 的一些新的變化和挑戰(zhàn),。下面介紹一下 DDR5 的驗(yàn)證和測(cè)試的一些問題和解決方案,。

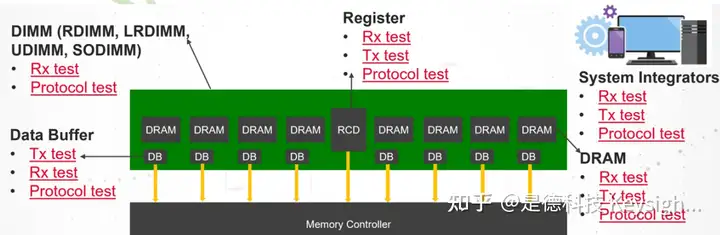

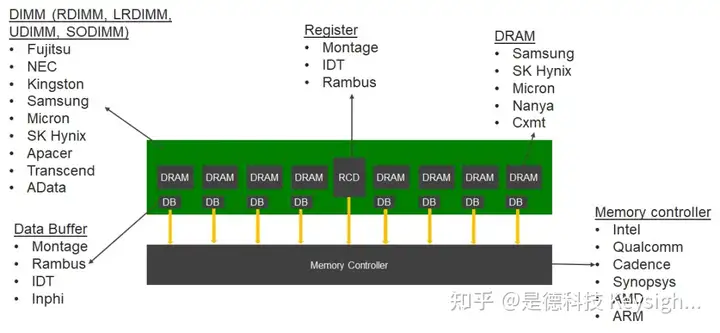

當(dāng)前 DDR5 規(guī)范尚未wanquan制定完畢,DDR5 顆粒以及輔助 DB 和 RCD 芯片目前主要還在 DIMM 應(yīng)用階段,,未進(jìn)入嵌入式系統(tǒng)階段。典型的 DDR5 生態(tài)系統(tǒng),,涉及 DDR5總線的主要包括 DIMM 產(chǎn)品和系統(tǒng)集成產(chǎn)品,。當(dāng)前主要有三種 DIMM 產(chǎn)品:UDIMM(Unbuffered DIMM),RDIMM(Registered DIMM),LRDIMM(Load-Reduced DIMM)。DDR5生態(tài)系統(tǒng)如下圖示:

圖 6 DDR5 生態(tài)系統(tǒng)

典型地在 DIMM 上,,與 DDR5總線相關(guān)除了核心的顆粒 DRAM 之外,,還有 DB(LRDIMM 上 用 buffer 芯片),,RCD 等芯片。從上圖可以看到針對(duì)不同功能的芯片部件到 DIMM 直到系統(tǒng)級(jí)產(chǎn)品 集成,,分別有不同的測(cè)試需求,。比如針對(duì) DRAM 顆粒以及 DB 和 RCD 等,需要進(jìn)行 TX,,RX 及 Protocol 測(cè)試,,而對(duì)整個(gè) DIMM 產(chǎn)品而言則要進(jìn)行 RX 測(cè)試和協(xié)議測(cè)試。

下面我們就 DDR5 DIMM產(chǎn)品各主要芯片或部件的 DDR5總線測(cè)試進(jìn)行一個(gè)簡(jiǎn)單介紹,。

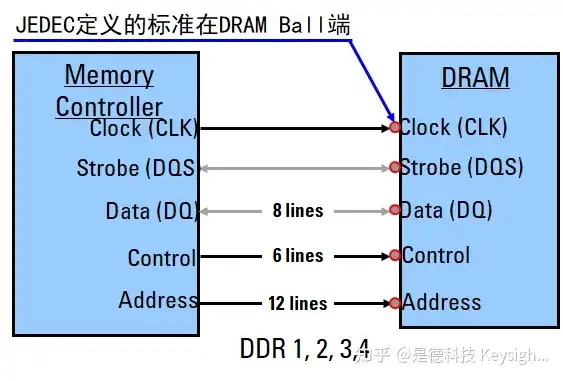

首先來看 DDR總線的發(fā)送端測(cè)試方法,。這一測(cè)試主要是以 DRAM 芯片為目標(biāo)進(jìn)行,從 DRAM 芯片到 Memory Controller 芯片乃至系統(tǒng)級(jí)產(chǎn)品開發(fā)均存在測(cè)試需求,。

探測(cè)問題

同其它標(biāo)準(zhǔn)一樣,,我們首先要明確測(cè)試點(diǎn)的位置。在 DDR總線上,,由于 CPU 作為系統(tǒng)核 心,,通常是沒有辦法預(yù)留測(cè)試點(diǎn)進(jìn)行焊接或者采用專用夾具在系統(tǒng)上進(jìn)行探測(cè)的。因此 DDR總線 的測(cè)試一般都選擇在 DRAM 顆粒側(cè)進(jìn)行,。當(dāng) Memory Controller 對(duì) DRAM 進(jìn)行寫操作時(shí),,寫信號(hào)經(jīng) 過一段走線到 DRAM, 在接收端進(jìn)行信號(hào)探測(cè),因此實(shí)際測(cè)試的是 CPU 或 Memory Controller 發(fā)送 到顆粒側(cè)的信號(hào),。反之進(jìn)行讀操作時(shí),,則從 DRAM 發(fā)出數(shù)據(jù)信號(hào)到 Memory Controller,因此是在 信號(hào)的發(fā)送端進(jìn)行探測(cè),,信號(hào)則可能存在反射問題,。通常 JEDEC 規(guī)范定義的讀寫操作的信號(hào)指標(biāo) 即為上述定義。

圖 7 DDR5 BGA Probe 和板上安裝示意圖

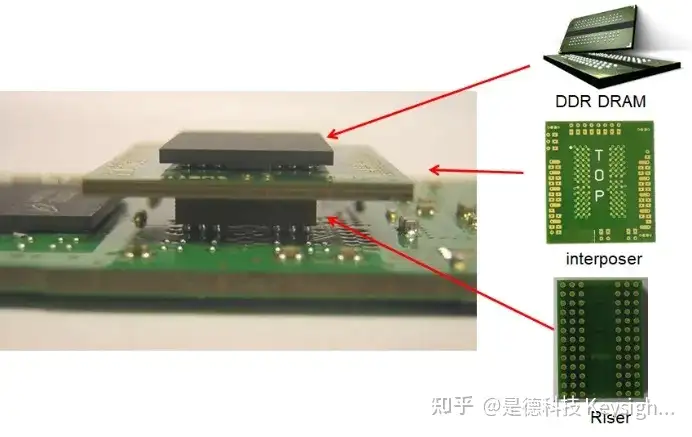

即使在顆粒側(cè)進(jìn)行測(cè)試,,在不同時(shí)代針對(duì)不同速率業(yè)界也采用過多種方法,。從早期的片外 電阻端接點(diǎn)到預(yù)留測(cè)試點(diǎn)和過孔,再發(fā)展到 DDR3 和 DDR4 時(shí)代廣泛采用的 BGA Probe----DDR 測(cè)試 專用夾具,。上圖即為 DDR5 BGA Probe 和板上安裝示意圖,,該 BGA Probe 適用于 DDR5-4800 X8 DRAM 顆粒。通過 BGA Probe 將各信號(hào)引到夾具邊緣,,然后用探頭焊接進(jìn)行測(cè)試,。這一測(cè)試點(diǎn)是 zui接近 DRAM BGA 焊球處的信號(hào),也就是說這一測(cè)試信號(hào)能夠準(zhǔn)確反映芯片對(duì)規(guī)范的遵從性,。

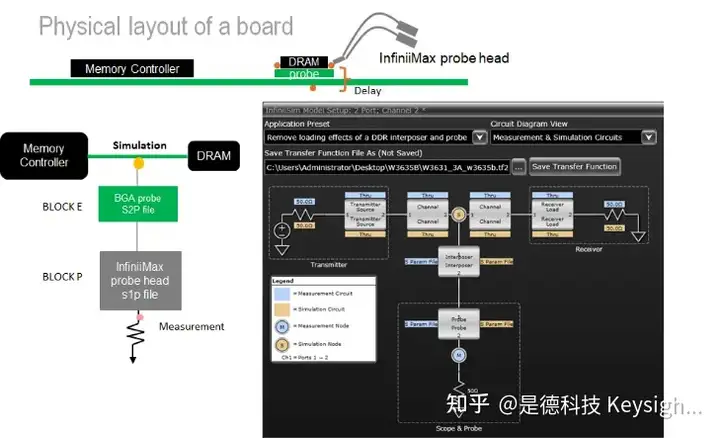

即使 BGA Probe 夾具已經(jīng)提供了zui接近真實(shí)信號(hào)測(cè)試點(diǎn)的位置,,然而依然存在誤差。因此 如果有 BGA Probe 的模型或 S 參數(shù),,還可以用示波器上的去嵌功能進(jìn)行 De-Embed 操作,。如下圖 示:

圖 8 InfiniiSim 用于 DDR BGA Probe 去嵌示意圖

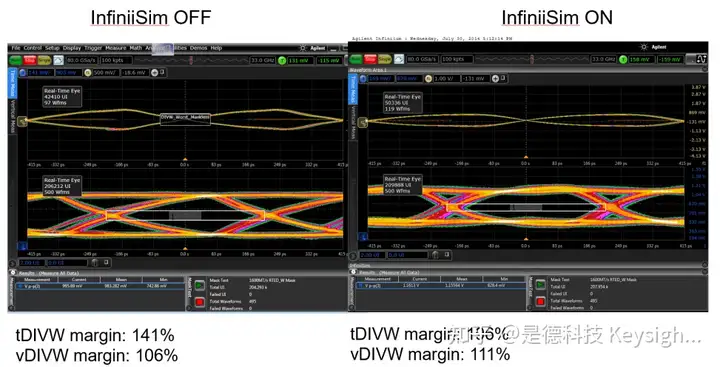

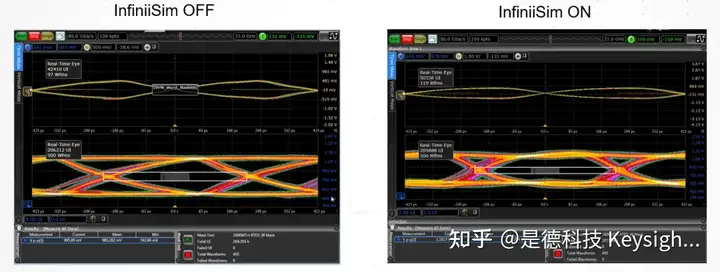

Keysight 實(shí)時(shí)示波器上的 D9020ASIA 選件中的 InfiniiSim 功能可以提供功能強(qiáng)大的去嵌,,下圖展示的是一個(gè) DDR4眼圖實(shí)測(cè)效果對(duì)比,采用 InfiniiSim 去嵌后眼圖在水平方向上裕量有顯著提高:

圖 9 InfiniiSim 去嵌功能與眼圖測(cè)試對(duì)比

Infiniium UXR-B 系列示波器

Infiniium UXR-B 系列示波器

在針對(duì) DDR信號(hào)的測(cè)試上,,示波器探頭選擇也是非常有講究的地方,。

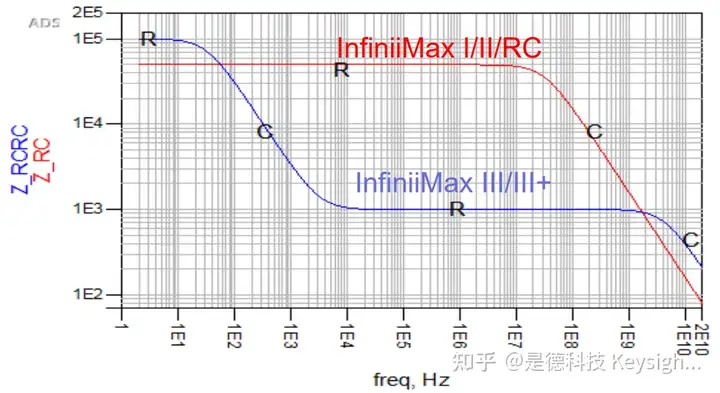

高帶寬有源探頭通常根據(jù)其負(fù)載模型有 RC(下圖中紅色跡線)和 RCRC(下圖中藍(lán)色跡線)的區(qū) 別,如下圖示,。Keysight 113X/116X 探頭均采用 RC模型,,表現(xiàn)為寬頻帶高阻抗特性。RCRC類探頭,,典型地如 N7000A 系列和 N280X 系列,,具有高 DC 阻抗,中頻帶阻抗則明顯低于 RC 探頭,,為 K? 級(jí),。

圖 10 RC 與 RCRC 探頭阻抗曲線示意圖

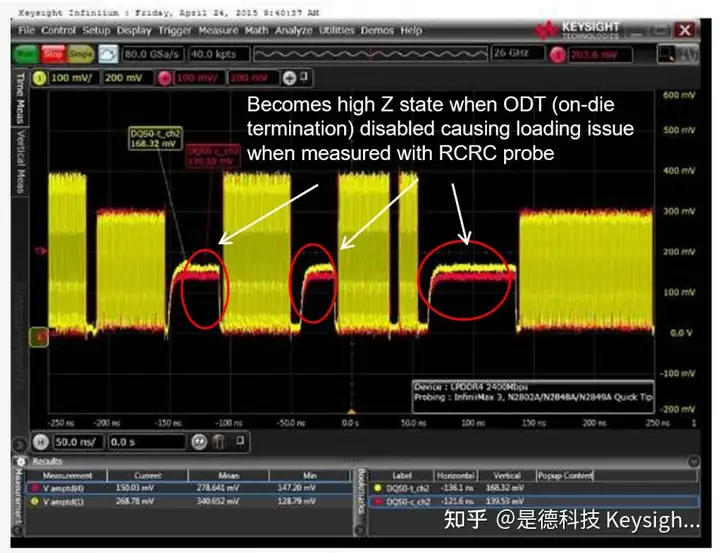

考慮到 DDR總線空閑時(shí)呈 High Z 狀態(tài),動(dòng)態(tài) ODT 使 DRAM 可以在高或低端接阻抗之間切 換,。 在 High Z 狀態(tài)端接阻抗變高時(shí),,探頭阻抗需要足夠高以降低探頭負(fù)載效應(yīng),探頭阻抗偏低對(duì)電路不能形成足夠高阻從而產(chǎn)生假信號(hào),。下面兩幅圖分別對(duì)比采用 RCRC探頭和 RC探頭進(jìn)行測(cè)試時(shí)的波形,。

圖 11 RCRC探頭和 RC探頭 DDR波形測(cè)試對(duì)比

除了探頭的阻抗特性外,考慮到 DDR5顆粒的體積越來越小帶來的封裝越來越小型化,,對(duì) 探頭前端尺寸的小型化要求也越來越高,。

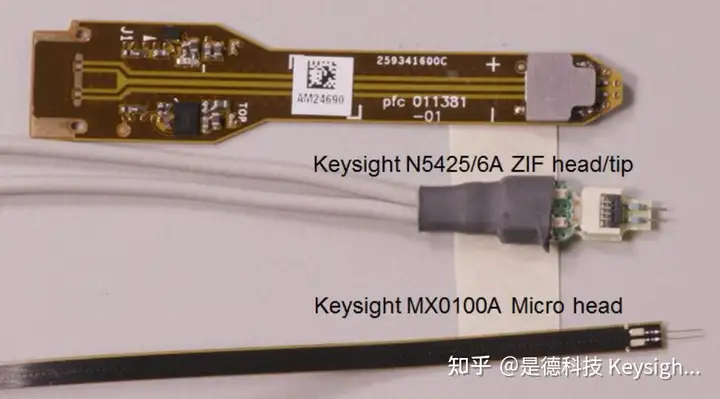

Keysight 最新推出的 MX0023A 25GHz 帶寬 RC 探頭,配合最新的 MX0100A 焊接前端,推薦 用于 DDR5 測(cè)試,。 MX0100A 前端間距在 0-7mm 范圍內(nèi)可調(diào)節(jié),,與 MX0023A 配合使用帶寬可達(dá) 25GHz,與 1169B 配合使用可達(dá) 13Ghz,。另外該前端工作范圍從-55 °C 到+155 °C,,支持進(jìn)行高低溫 測(cè)試(配合長(zhǎng)達(dá) 1 米的 N5450B 高低溫延長(zhǎng)電纜)。

MX0025A InfiniiMax Ultra 探頭放大器,,25 GHz

圖 12 Keysight MX0023A RC 探頭和 MX0100A 焊接前端及業(yè)界其它廠家前端尺寸對(duì)比

重點(diǎn):采用 RC 類型探頭對(duì) DDR總線進(jìn)行探測(cè)是確保獲得精確測(cè)量的基礎(chǔ)保障,。

2. DDR總線測(cè)試的難點(diǎn) - 讀寫分離問題

讀寫分離一直是 DDR總線測(cè)試的難點(diǎn)。由于 DDR總線一直采用讀寫數(shù)據(jù)共享數(shù)據(jù)總線,, 而 JEDEC 規(guī)范針對(duì)讀寫操作制定了不同的指標(biāo),,因此如果需要對(duì)被測(cè)器件和設(shè)備進(jìn)行準(zhǔn)確測(cè)試就 必須分別對(duì)讀和寫進(jìn)行分開測(cè)試。一種方法是 Memory Controller 可以編程只進(jìn)行讀或?qū)懖僮饕苑?別進(jìn)行測(cè)試,。另外一種方法就是在示波器上根據(jù)讀和寫信號(hào)的特點(diǎn)設(shè)置恰當(dāng)?shù)挠|發(fā)進(jìn)行分離,。我 們來看看第二種方法。

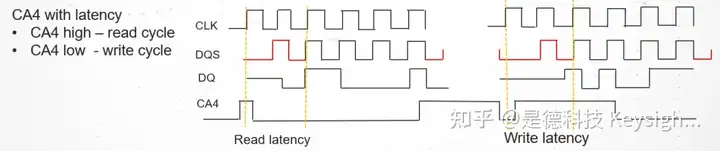

在過往 DDR3 和 DDR4總線上,,主要采用 DQS 前導(dǎo)位或者 DQS 和 DQ 的相位差進(jìn)行分離,。 在 DDR5總線上,DQS 和 DQ 在讀寫操作時(shí)沒有相位差,,DQS 的讀寫操作的前導(dǎo)碼也是相同的,, 因此在 DDR5總線上的讀寫分離是一個(gè)難點(diǎn)。

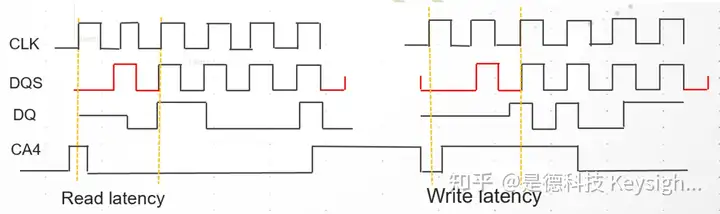

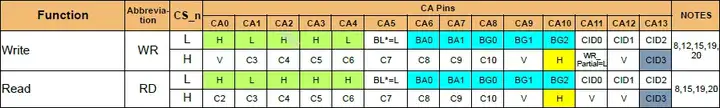

當(dāng)前 Keysight 根據(jù) JEDEC DDR5 規(guī)范真值表,,在讀和寫操作時(shí),,CA4 有差異,如下圖紅色方 框標(biāo)準(zhǔn),,讀時(shí)高,,寫時(shí)低。另外再根據(jù)讀和寫操作時(shí)的 Latency 差異進(jìn)行讀寫分離,。

Command Truth Table

表 2 JEDEC 規(guī)范命令真值表

圖 13 DDR5總線讀寫時(shí)序和 Latency 差異

重點(diǎn):如果要對(duì) DDR5總線的讀寫操作進(jìn)行有效分離,,相比以往DDR標(biāo)準(zhǔn)采用最少 3 根探頭 (CLK,DQS,DQ)進(jìn)行信號(hào)測(cè)試連接,在 DDR5 則需要增加 CA4 連接和探測(cè),,也就是說需要 4根探頭進(jìn)行測(cè)試,!

3.信號(hào)分析和算法方面的變化 DDR5 相比以往DDR標(biāo)準(zhǔn)在時(shí)鐘和控制及數(shù)據(jù)信號(hào)的分析等也有很多進(jìn)展。

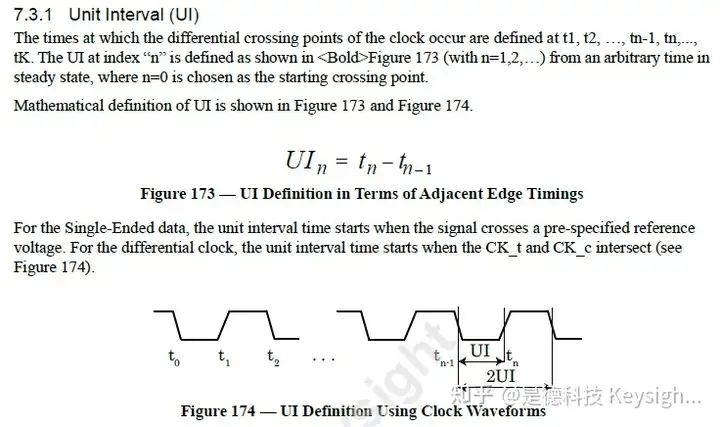

首先來看全新的抖動(dòng)定義,。

全新的抖動(dòng)定義

考慮到 DDR5全速率時(shí)鐘架構(gòu),,因此在 DQS/DQ/CLK 等信號(hào)抖動(dòng)的測(cè)量上相比以往DDR標(biāo)準(zhǔn)提出了新的定義。

抖動(dòng)基礎(chǔ)知識(shí):抖動(dòng)源,、類型和特征

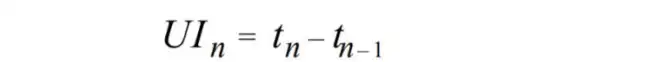

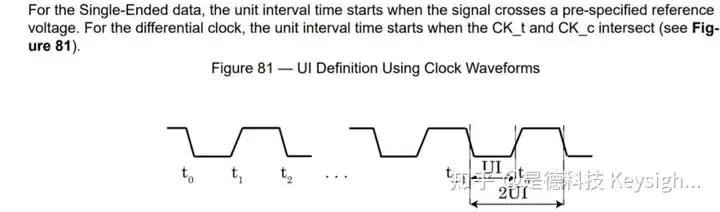

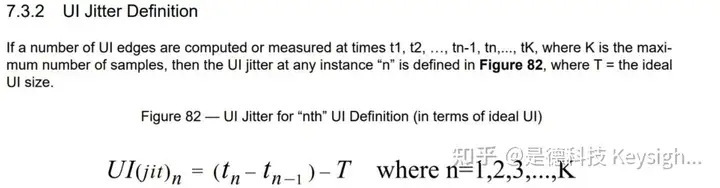

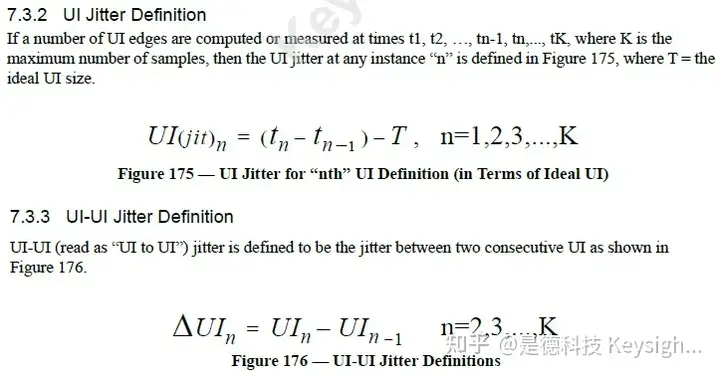

圖 14 DDR5 規(guī)范中 UI定義

特別地,,對(duì)時(shí)鐘而言,一個(gè)周期計(jì)作 2 個(gè) UI.

圖 15 UI Jitter 定義

UI Jitter 定義為任一個(gè)周期相對(duì)理想值的偏差,,類似于經(jīng)典抖動(dòng)定義中的 Period Jitter,,周期抖動(dòng)。

UI-UI Jitter 則類似于經(jīng)典抖動(dòng)定義中的 Period-Period Jitter,,是 UI 的微分,。

而 Accumulated Jitter 則類似于經(jīng)典抖動(dòng)定義中的 TIE Jitter,時(shí)間間隔誤差抖動(dòng),,是長(zhǎng)期抖動(dòng)的積分,。

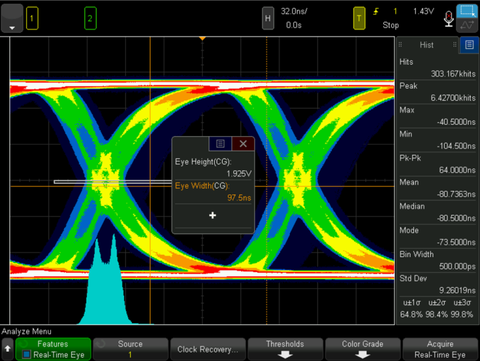

– 可以測(cè)量數(shù)據(jù)眼高和眼寬

– 用戶還可以根據(jù)器件規(guī)范定義自己的眼圖模板

– 如果眼圖不符合模板,那么一致性應(yīng)用軟件可以報(bào)告不合格狀態(tài)

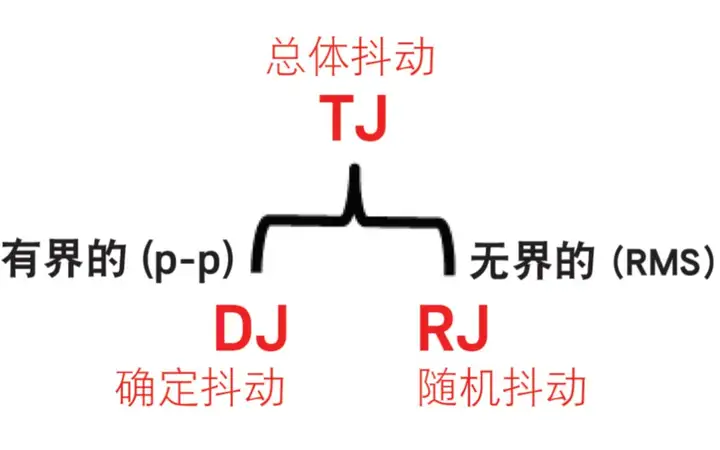

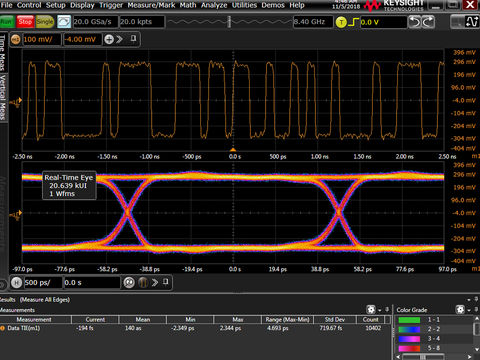

DDR4 規(guī)范考慮了抖動(dòng)和 BER 的關(guān)鍵作用,。計(jì)算抖動(dòng) BER 測(cè)量結(jié)果很重要,,它可以統(tǒng)計(jì)測(cè)量總體抖動(dòng)(確定性抖動(dòng)+隨機(jī)抖動(dòng)),了解設(shè)計(jì)的數(shù)據(jù)有效窗口結(jié)果和可能出現(xiàn)錯(cuò)誤的概率,。

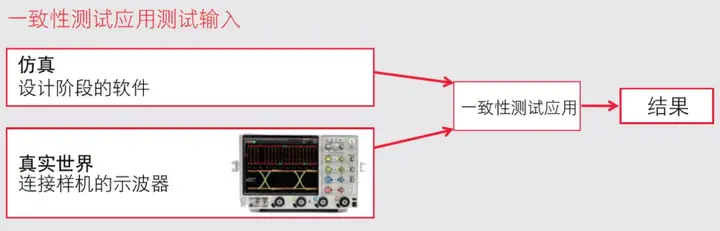

除了規(guī)范測(cè)試,,采用正確的測(cè)試過程和方法也是至關(guān)重要的。例如,,示波器探頭的正確放置會(huì)影響一致性測(cè)試結(jié)果以及設(shè)計(jì)裕量的準(zhǔn)確表征和測(cè)試,。對(duì)于 JEDEC 規(guī)范,,最佳探測(cè)點(diǎn)位于 DRAM封裝的球上(不在傳輸線或通道上,也不在存儲(chǔ)器控制器上),。

仿真是測(cè)試過程中的另一個(gè)重要卻經(jīng)常被忽略的步驟,。隨著總線速度的提高以及獲得盡量多裕量的需求,仿真過程可以很大程度地幫助減少設(shè)計(jì)周期和成本,。

例如,,仿真有助于確保系統(tǒng)能夠容忍內(nèi)插器的負(fù)載效應(yīng)。這一步驟評(píng)測(cè)所測(cè)量的帶寬/頻率響應(yīng),,確保內(nèi)插器不會(huì)斷開總線,。

最后,是德科技與 JEDEC 組織密切合作,,以確保其測(cè)試和測(cè)量解決方案與 JEDEC 標(biāo)準(zhǔn)的測(cè)試和測(cè)量規(guī)范保持高度一致,。

圖 2. 然后將具有適當(dāng)負(fù)載效應(yīng)的仿真設(shè)計(jì)與原型的實(shí)際掃描結(jié)果進(jìn)行比較,確定系統(tǒng)正常運(yùn)行,。

眼圖測(cè)試

確定性抖動(dòng)(DJ)通常是有界而可預(yù)測(cè)的,可以與數(shù)據(jù)流相關(guān)聯(lián),,例如符號(hào)間干擾和占空比失真,。隨機(jī)抖動(dòng)(RJ)屬于高斯分布并且是無界的。與任何高斯分布一樣,,隨著總量的增加,,分布的峰-峰值也會(huì)增加。因此,,總體抖動(dòng)(TJ)等于確定性抖動(dòng) DJ 加上隨機(jī)抖動(dòng) RJ 與 BER乘積,。了解抖動(dòng)的組成和來源可以幫助設(shè)計(jì)人員降低設(shè)計(jì)中抖動(dòng)的發(fā)生率,確保更好的數(shù)據(jù)性能,。

3.1 發(fā)送端TX測(cè)試挑戰(zhàn)

3.1.1 讀寫分離

由于規(guī)范規(guī)定DDR5,不再像傳統(tǒng)的DDR一樣,,讀寫在pin腳處有嚴(yán)格的相位差別,。所以使用DQS-DQ 相位差和前置信號(hào)模式的傳統(tǒng)方法可能不再適用,需要采用新方法進(jìn)行讀寫數(shù)據(jù)分離,。

根據(jù)真值表可以看出,,CA4在讀寫操作過程中有不同的邏輯電平,所以可以根據(jù)CA4的狀態(tài)來結(jié)合讀寫延遲來進(jìn)行讀寫分離,。

3.1.2新增的測(cè)試參數(shù)

由于速率的提高,,可能需要新的測(cè)試參數(shù)來鑒定關(guān)鍵信號(hào)。抖動(dòng)成為關(guān)鍵信號(hào)的重要組成部分。規(guī)范定義了全新的UI抖動(dòng)定義,。

以及針對(duì)該UI的測(cè)量算法,。

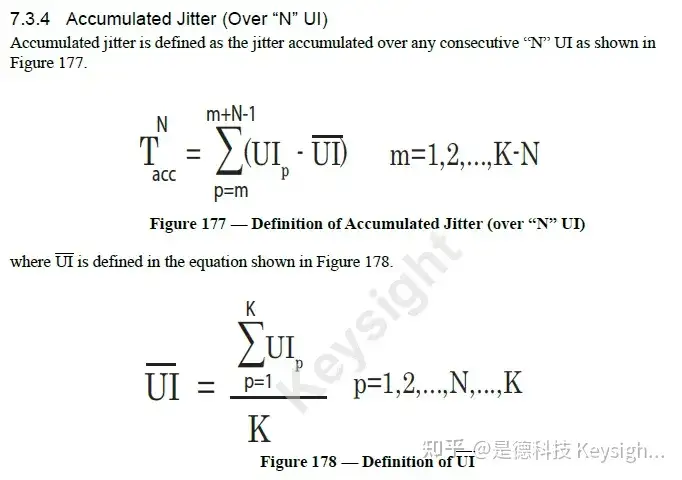

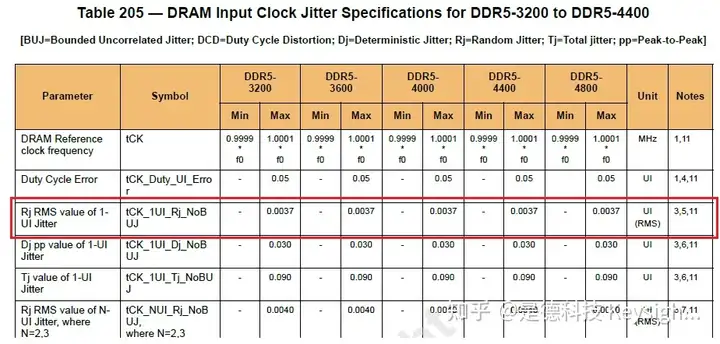

UI的測(cè)量項(xiàng)將覆蓋CLK(input)、DQS(tx)和DQ(tx) 信號(hào),,且要求非常嚴(yán)格,。

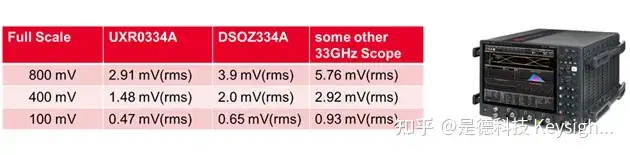

根據(jù)下表的計(jì)算,按照DDR5 4800的速率為例,,要求測(cè)量出來的Rj最大值為0.0037UI,也就是769.6fs,。

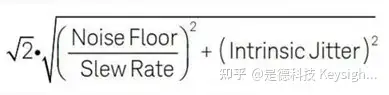

如此高要求的測(cè)量結(jié)果,,也對(duì)儀表本身的性能提出了非常高的要求。儀表的抖動(dòng)測(cè)量本底計(jì)算公式如下,,可以看出示波器的本底噪聲以及本底抖動(dòng),,對(duì)抖動(dòng)測(cè)量起了非常大的影響。

是德科技UXR旗艦級(jí)實(shí)時(shí)示波器,,具有25fs的極低本底抖動(dòng),,165μV(rms)(16G帶寬下) 的本底噪聲??梢蕴峁┛煽康腄DR5的相關(guān)抖動(dòng)測(cè)試,。

實(shí)時(shí)示波器――合規(guī)性測(cè)試

3.1.3 測(cè)試方法

DDR的TX測(cè)量手法,一直是我們所關(guān)心的內(nèi)容,。在DDR4以前,,規(guī)范規(guī)定的測(cè)試點(diǎn),均在DRAM的ball處,。DDR5里,,除了眼圖測(cè)試以外,其他測(cè)試點(diǎn)沒有做額外更新,。

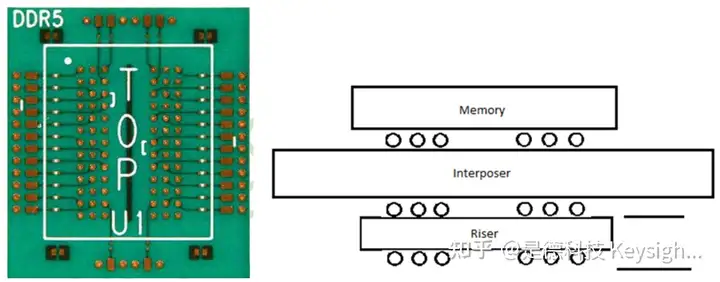

我們推薦使用interposer的方式來進(jìn)行測(cè)量,,如下圖所示。

測(cè)量完成后,,通過S參數(shù)的數(shù)學(xué)計(jì)算,,實(shí)現(xiàn)從實(shí)測(cè)點(diǎn)到理論測(cè)試點(diǎn)的波形轉(zhuǎn)換。

而針對(duì)于DDR5的眼圖測(cè)試,,如果打開了DFE功能,,示波器可以在去嵌的基礎(chǔ)上,進(jìn)一步完成均衡的操作,,最后得到需要的波形,。

當(dāng)然,是德科技已經(jīng)提供自動(dòng)化的測(cè)試App,方便的給用戶提供可視化的一鍵測(cè)試方案,。

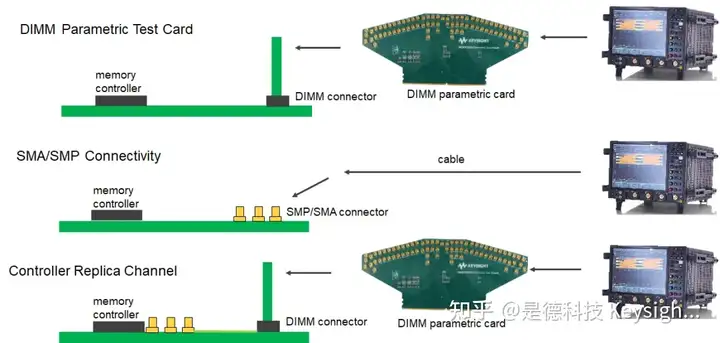

3.1.4 控制器測(cè)試新場(chǎng)景

由于信號(hào)速率的不斷提升,,控制器、鏈路,、芯片,,紛紛加入了測(cè)試大軍。下圖展示了針對(duì)于控制器,、PCB互聯(lián)鏈路的TX測(cè)試場(chǎng)景,,通過示波器,配合夾具的使用,,來實(shí)現(xiàn)發(fā)送端的信號(hào)質(zhì)量測(cè)試,。

3.2.1 接收端新技術(shù)

以往的高速串行鏈路設(shè)計(jì)中,我們知道隨著速率的不斷提升,,鏈路的損耗,,以及ISI,對(duì)高頻分量的影響越來越大,,所以在PCIE Gen3的時(shí)候,,引入了接收端均衡的概念,用于彌補(bǔ)高頻分量的損失,。

具體來看,,有下面幾點(diǎn)。①是接收端的信號(hào)會(huì)先經(jīng)過CTLE(連續(xù)時(shí)間線性均衡)均衡,,圖上展示的是具有7個(gè)DC gain的CTLE曲線,。然后信號(hào)會(huì)一分為二,一部分給到CDR②,,CDR中的核心PLL的OJTF函數(shù)是一個(gè)類似左邊的高通濾波器,。信號(hào)的另一部分信號(hào)會(huì)給到③具有一個(gè)tap的DFE(panjue反饋均衡)。

我們特別注意一下圖里標(biāo)識(shí)的2個(gè)測(cè)試點(diǎn),,一個(gè)是TP2,,一個(gè)是TP2`。通常TP2是使用示波器真實(shí)捕獲到的信號(hào),,而TP2`則是使用標(biāo)準(zhǔn)的參考接收機(jī)模型,,來去復(fù)原芯片真實(shí)看到的波形。那這種均衡技術(shù)對(duì)DDR5是否有參考借鑒的意義呢,?

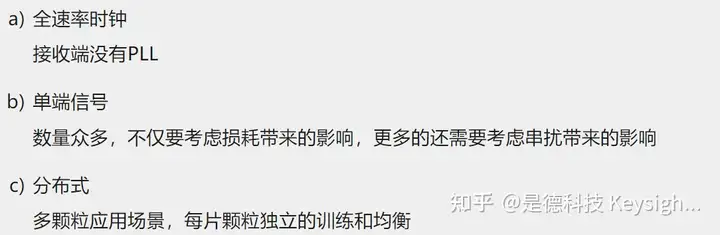

首先看一下DDR5相對(duì)于傳統(tǒng)serdes技術(shù)有什么特殊的地方,。

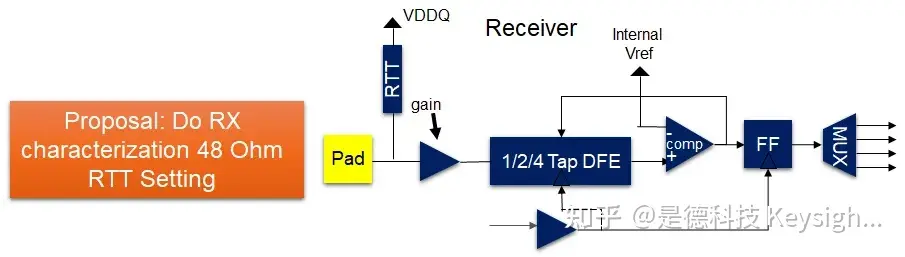

了解了DDR5和傳統(tǒng)Serdes的幾個(gè)特別之處外,參考在PCIE上使用的均衡技術(shù),,進(jìn)行了部分調(diào)整后如下,。

首先是CDR,由于系統(tǒng)里有了顯示時(shí)鐘,可以使用不具有頻率跟蹤能力的DLL模塊,,來代替原先復(fù)雜的CDR模塊,。

第二個(gè)是CTLE,雖然CTLE實(shí)現(xiàn)簡(jiǎn)單,,但是考慮到單端的DDR5總線里的反射和串?dāng)_等,,對(duì)信噪比惡化嚴(yán)重,所以使用了VGA可變?cè)鲆娣糯笃鱽泶鍯TLE,。

第三個(gè)是借鑒了成熟的DFE均衡技術(shù),。最后一個(gè),沿用了DDR以往的write leveling和read leveling機(jī)制,。把原先在接收端實(shí)現(xiàn)的去加重功能放在了控制器端來實(shí)現(xiàn),。

3.2.2 接收端測(cè)試的新挑戰(zhàn)

傳統(tǒng)的Serdes接收端測(cè)試(以PCIe為例),目的是確定DUT能否在芯片封裝的ball處(或者CEM規(guī)范的金手指處)可靠接收帶有zhidin受損的信號(hào),,達(dá)到要求的誤碼率要求。

針對(duì)DDR的單端并行總線系統(tǒng),,非相關(guān)抖動(dòng),、電平干擾、ISI,、串?dāng)_,、反射,對(duì)于系統(tǒng)的可靠運(yùn)行至關(guān)重要,。DDR5的接收端測(cè)試,,不僅包括了壓力眼測(cè)試,也就是在給定的壓力眼信號(hào)下,,達(dá)到特定的誤碼率要求,,還包括了幅度電壓方面和水平抖動(dòng)方面的靈敏度測(cè)試。

而被測(cè)DUT,,可以是控制器,、DRAM、緩沖器/寄存器,、DIMM 等,。

3.2.3 接收端測(cè)試的新方法

規(guī)范定義了接收端測(cè)試?yán)锏乃袦y(cè)試點(diǎn)要求,以及波形在均衡器之后的指標(biāo)要求,。測(cè)試前,,需要按照規(guī)范的要求進(jìn)行校準(zhǔn)。

校準(zhǔn)之前,,考慮到DDR總線的特殊性,。ODT 會(huì)用于優(yōu)化發(fā)送端到接收端的信號(hào)質(zhì)量,由于其允許不同的阻抗設(shè)置,接收端測(cè)試過程中,,建議使用 48 歐姆進(jìn)行校準(zhǔn),,以盡量減少與標(biāo)準(zhǔn)測(cè)試設(shè)備之間的不匹配。在此假設(shè)下,,通過電平和抖動(dòng)的 BERT 設(shè)置來調(diào)整信號(hào)的形狀,,實(shí)現(xiàn)壓力信號(hào)的產(chǎn)生。

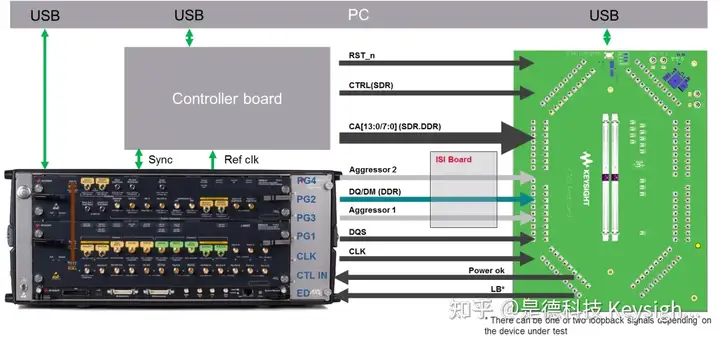

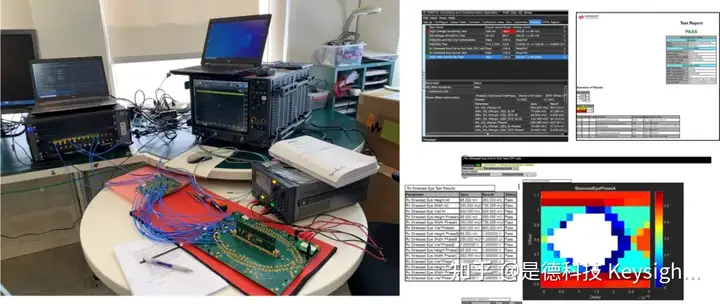

是德科技提供以M8000系列誤碼儀為基礎(chǔ)的DDR5接收端測(cè)試方案,,支持控制器,、DRAM、緩沖器/寄存器,、DIMM的測(cè)試,。

3.2.4 接收端測(cè)試的校準(zhǔn)

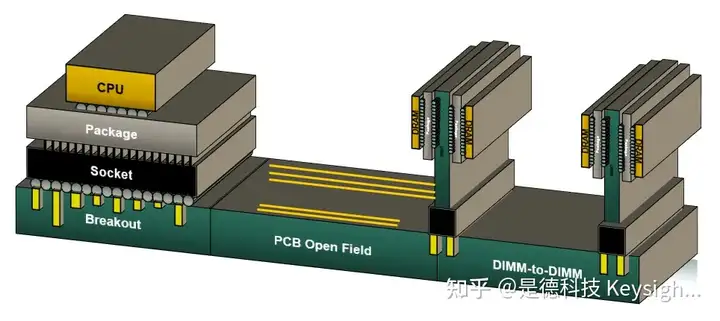

下圖是DDR在系統(tǒng)產(chǎn)品中實(shí)際應(yīng)用的拓?fù)浣Y(jié)構(gòu)。依次從DDR控制器,,經(jīng)過PCB路徑,,來到DIMM上的DRAM顆粒。

DDR在系統(tǒng)產(chǎn)品中實(shí)際應(yīng)用的拓?fù)浣Y(jié)構(gòu)

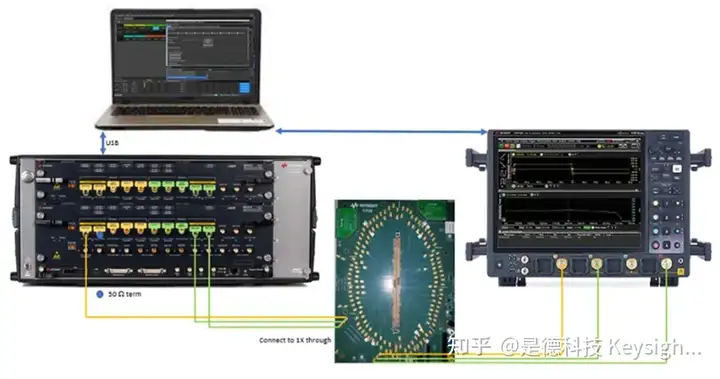

做校準(zhǔn)的時(shí)候,,也是參考上圖的拓?fù)鋪硗瓿烧麄€(gè)路徑的模擬,。針對(duì)DIMM或者顆粒而言,信號(hào)由BERT發(fā)出,,經(jīng)過CTC2 Board和replicate card,,最終由示波器接收,組成完整的端到端鏈路,。

這里要特別說明的是,,針對(duì)不同的產(chǎn)品測(cè)試,有對(duì)應(yīng)的夾具來進(jìn)行配合,。主要的夾具有如下幾種,。分別是下圖中的C2C test card,System Motherboard Test Fixture,,Device Validation Fixture,。

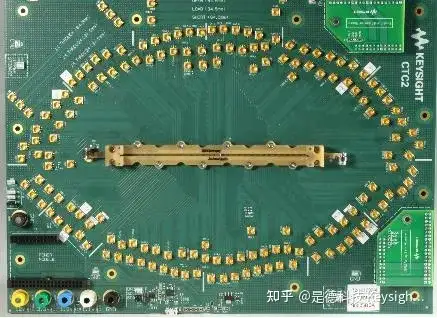

其中,CTC2 test card提供DIMM插座,,同時(shí)將DIMM上所有信號(hào)包括CA/CMD,、DQS,DQ通過SMP連接器的形式引出,。用于DIMM,、RCD測(cè)試夾具、Data Buffer測(cè)試夾具,、DRAM測(cè)試夾具等的校準(zhǔn)和測(cè)試,。

CTC2 test card

System Motherboard Test Fixture也同樣把CA/CMD,、DQS,DQ的信號(hào)通過SMP的方式引出,,用于控制器的發(fā)送端測(cè)試,,以及控制器的接收端測(cè)試校準(zhǔn)和測(cè)試,同時(shí)還支持系統(tǒng)主板的通道特性驗(yàn)證,。

System Motherboard Test Fixture

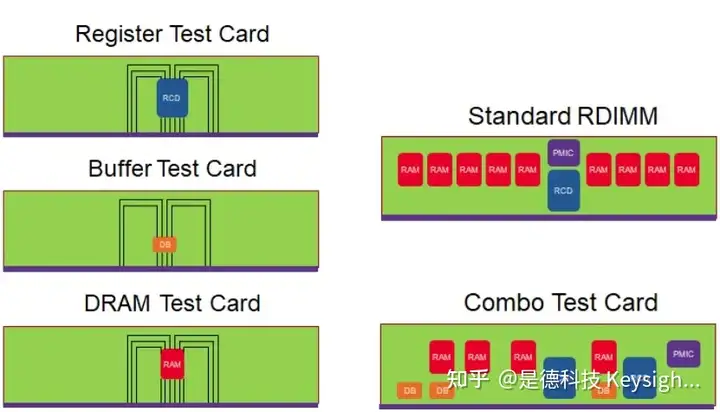

Device Validation Fixture包括了RCD的測(cè)試夾具,,Data Buffer的測(cè)試夾具,DRAM的測(cè)試夾具,,以及Combo測(cè)試夾具等,。主要用于單個(gè)器件產(chǎn)品的校準(zhǔn)與測(cè)試,以及多器件的校準(zhǔn)與測(cè)試,。測(cè)試時(shí)插在CTC2的test card上,。

Device Validation Fixture

下圖展示的是基于CTC2 test card進(jìn)行的校準(zhǔn)操作。連接方式如圖所示,。

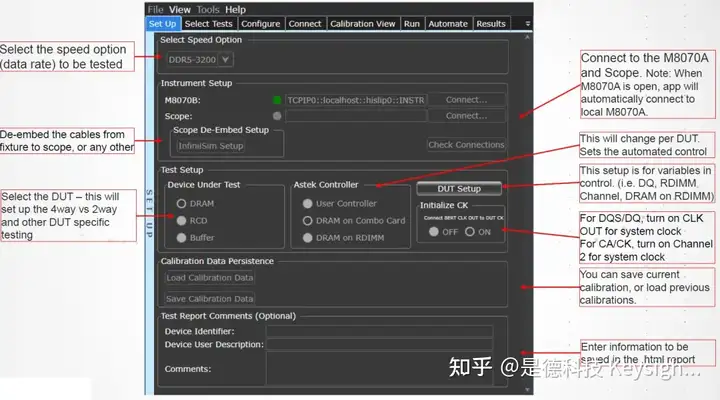

使用M80885RCA自動(dòng)化軟件,,根據(jù)向?qū)В瓿蓽y(cè)試環(huán)境參數(shù)的setup,,并對(duì)DUT進(jìn)行初始化,。

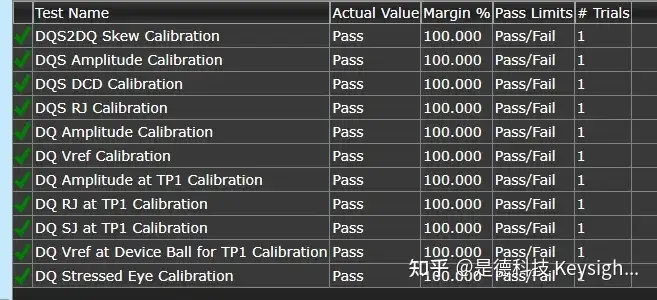

一步一步,實(shí)現(xiàn)DQS&DQ和CK&CA的各參數(shù)自動(dòng)化校準(zhǔn),。完成自動(dòng)化校準(zhǔn)后,可以查看每個(gè)校準(zhǔn)項(xiàng)目的測(cè)試結(jié)果,,如下圖所示,。

3.2.5 接收端測(cè)試

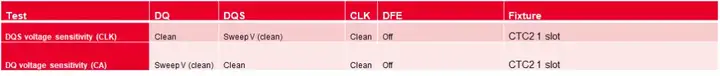

接收端測(cè)試包括兩大部分測(cè)試內(nèi)容,Sensitivity測(cè)試和Stressed Eye測(cè)試,。其中Sensitivity測(cè)試又包含Voltage Sensitivity和Jitter Sensitivity,。

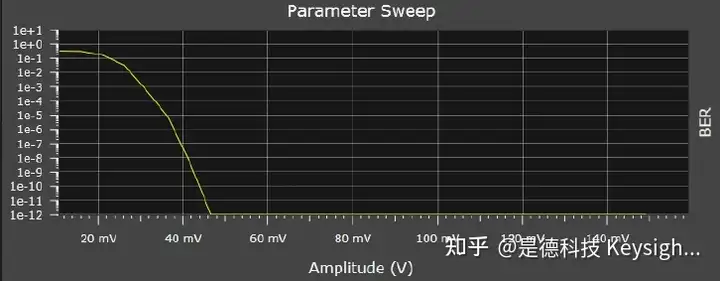

DQS和DQ的Voltage Sensitivity測(cè)試中,測(cè)試DQS的時(shí)候保持DQ的信號(hào)不變,,測(cè)試DQ的時(shí)候保持DQS的信號(hào)不變,。不斷調(diào)整另外一個(gè)參數(shù)的變量,遍歷整個(gè)參數(shù)的范圍后,,統(tǒng)計(jì)誤碼率,。

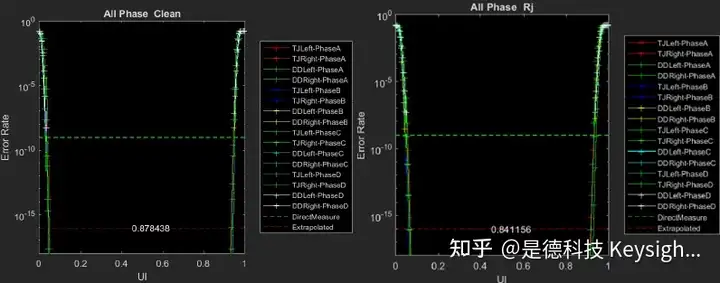

DQS的Jitter Sensitivity測(cè)試中,首先輸出clean的clk和dq,。在此基礎(chǔ)上,,遍歷DQS和DQ的相位,計(jì)算出本底jitter的Sensitivity測(cè)試,。然后依次改變DCD和Rj以及DCD和Rj的組合,,遍歷DQS和DQ的相位,,完成各種場(chǎng)景下的jitter Sensitivity測(cè)試。

Stressed Eye測(cè)試中,,使用校準(zhǔn)過程中的壓力信號(hào)(如下圖),,來進(jìn)行環(huán)回誤碼率測(cè)試。

測(cè)試完成后,,M80885一致性軟件會(huì)給出上圖右側(cè)的測(cè)試結(jié)果與測(cè)試報(bào)告,。

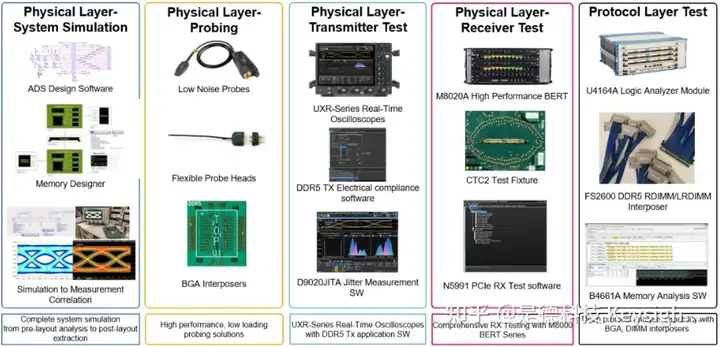

是德科技可以給大家?guī)硗暾亩说蕉私鉀Q方案,。包括設(shè)計(jì)前期的仿真,,涵蓋了memory designer的建模和ADS的前后仿真。發(fā)送端測(cè)試中,,我們提供業(yè)內(nèi)旗艦級(jí)性能指標(biāo)的UXR實(shí)時(shí)示波器和高性能的RC模型探頭,,有效降低測(cè)試負(fù)載。接收端測(cè)試中,,我們提供all-in-box的M8000系列誤碼儀,,支持控制器、DRAM,、Data Buffer,、RCD、DIMM的接收端校準(zhǔn)與測(cè)試,。協(xié)議分析儀方面,,U4164A系列,支持完整的DDR,、LPDDR的協(xié)議解碼測(cè)試,。

(空格分隔,最多3個(gè),單個(gè)標(biāo)簽最多10個(gè)字符)

立即詢價(jià)

您提交后,,專屬客服將第一時(shí)間為您服務(wù)